## **Bruce R. Archambeault**

**Contributions by James L. Drewniak**

## PCB DESIGN FOR REAL-WORLD EMI CONTROL

### THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

# PCB DESIGN FOR REAL-WORLD EMI CONTROL

by

### **Bruce R. Archambeault**

IBM Corporation Research Triangle Park, NC

Springer Science+Business Media, LLC

Electronic Services <a href="http://www.wkap.nl">http://www.wkap.nl</a>

ISBN 978-1-4757-3642-7 ISBN 978-1-4757-3640-3 (eBook) DOI 10.1007/978-1-4757-3640-3

#### Library of Congress Cataloging-in-Publication Data

Archambeault, Bruce.

PCB design for real-world EMI control / by Bruce R. Archambeault.

p. cm.-- (The Kluwer international series in engineering and computer science; SECS 696) Includes bibliographical references and index.

1. Printed circuits—Design and construction. 2. Electromagnetic interference—Prevention. I. Title. II. Series.

TK7868.P7 A72 2002 621.3815'31--dc21

2002073021

Copyright © 2002 by Springer Science+Business Media New York

Originally published by Kluwer Academic Publishers. Second Printing 2004. Softcover reprint of the hardcover 1st edition 2004

This printing is a digital duplication of the original edition.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording, or otherwise, without the prior written permission of the publisher, Springer Science+Business Media, LLC

Printed on acid-free paper.

## Dedication

This book is dedicated to my wife, best friend, and the person who is the center of my universe, Susan Archambeault.

## Contents

| 1 | Introduction to EMI/EMC Design<br>for Printed Circuit Boards | 1  |

|---|--------------------------------------------------------------|----|

|   | 1.1 Introduction to EMI/EMC                                  | 1  |

|   | 1.2 EMI Emissions Sources                                    | 4  |

|   | 1.3 Inductance                                               | 5  |

|   | 1.4 "Ground"                                                 | 6  |

|   | 1.5 Shielding                                                | 6  |

|   | 1.6 Summary                                                  | 7  |

| 2 | EMC Fundamentals                                             | 9  |

|   | 2.1 Introduction                                             | 9  |

|   | 2.2 Coupling Mechanisms                                      | 10 |

|   | 2.2.1 Electric Field Coupling                                | 10 |

|   | 2.2.2 Magnetic Field Coupling                                | 12 |

|   | 2.3 Signal Spectra                                           | 14 |

|   | 2.3.1 Clock Signals' Harmonic Frequencies                    | 14 |

|   | 2.3.2 Hertz vs. Bits-per-Second                              | 17 |

|   | 2.3.3 Non-Squarewave Data Signals                            | 18 |

|   | 2.4 Resonance Effects                                        | 19 |

|   | 2.4.1 Magic and Luck                                         | 20 |

|   | 2.5 Potential Emissions Sources                              | 21 |

|   | 2.5.1 Shielded Products                                      | 21 |

|   | 2.5.2 Unshielded Products                                    | 22 |

|   | 2.6 Intentional Signal Content                               | 23 |

|   | 2.7 Summary                                                  | 23 |

## **3** What is Inductance?

| 3.1 | Introduction                          | 25 |

|-----|---------------------------------------|----|

| 3.2 | Electromagnetic Induction             | 25 |

| 3.3 | Mutual Inductance                     | 27 |

| 3.4 | Self-Inductance                       | 29 |

|     | 3.4.1 Self-Inductance per Unit Length | 33 |

| 3.5 | Partial Inductance                    | 36 |

| 3.6 | Summary                               | 40 |

|     |                                       |    |

25

## 4 The Ground Myth 43

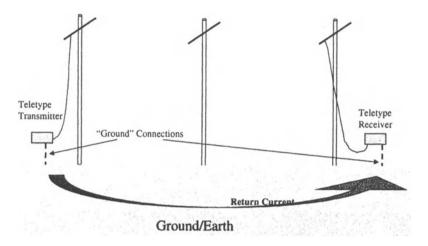

| 4.1 Where Did The Term "Ground" Originate? | 43 |

|--------------------------------------------|----|

| 4.2 What Do We Mean When We Say "Ground"?  | 46 |

| 4.2.1 Signal Reference                     | 46 |

| 4.2.2 Power Reference                      | 49 |

| 4.2.3 Chassis Reference                    | 50 |

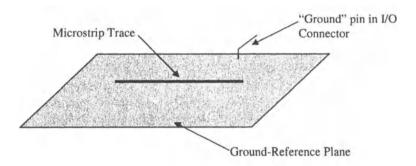

| 4.2.4 Unshielded Cables                    | 51 |

| 4.2.5 Shielded Cables                      | 54 |

| 4.2.6 Earth Safety Reference               | 55 |

| 4.3 'Ground' is Not a Current Sink         | 55 |

| 4.4 Referencing Strategies                 | 55 |

| 4.4.1 Single-Point Ground-Reference        |    |

| Strategy                                   | 56 |

| 4.4.2 Multi-Point Ground-Reference         |    |

| Strategy                                   | 56 |

| 4.5 Grounding Heatsinks to PC boards       | 58 |

| 4.5.1 Heatsink "Grounding" Example         | 61 |

| 4.6 PCB Reference Connection to Chassis    |    |

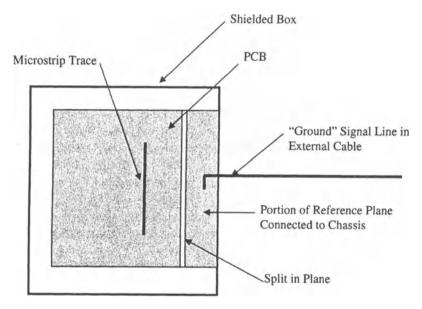

| Reference                                  | 64 |

| 4.6.1 I/O Area Connection                  | 64 |

| 4.7 Summary                                | 66 |

viii

| 5 | Return Current Design                        | 69  |

|---|----------------------------------------------|-----|

|   | 5.1 Introduction                             | 69  |

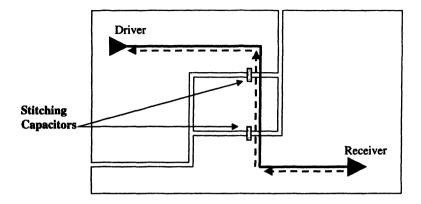

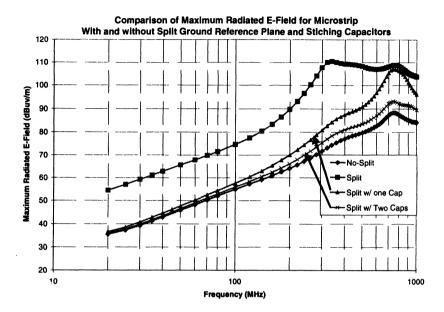

|   | 5.2 Split Reference Planes                   | 71  |

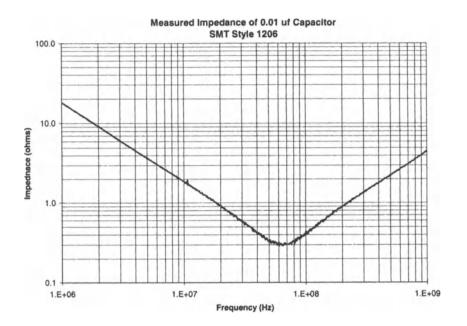

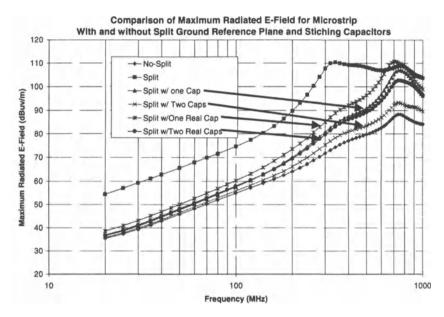

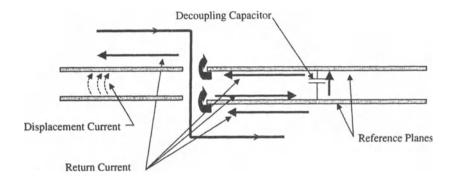

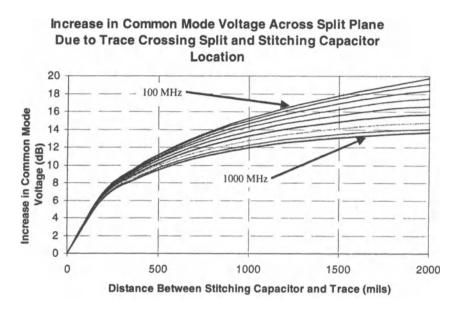

|   | 5.2.1 Stitching Capacitors                   | 72  |

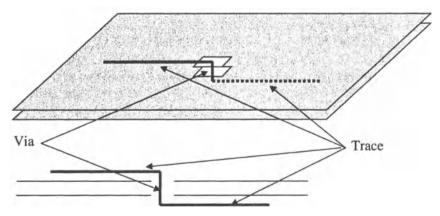

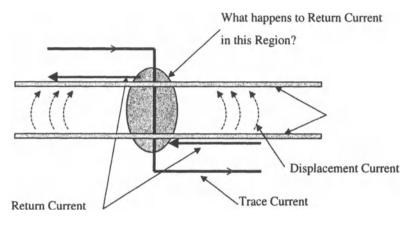

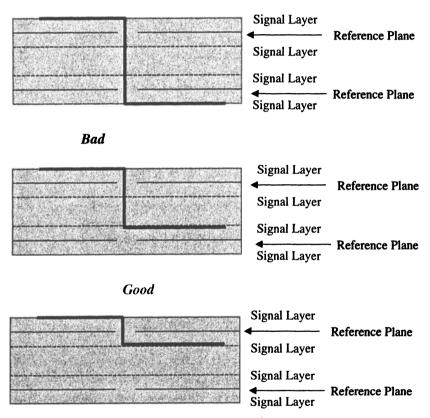

|   | 5.3 Trace Changing Reference Planes          | 76  |

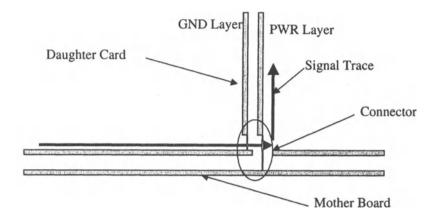

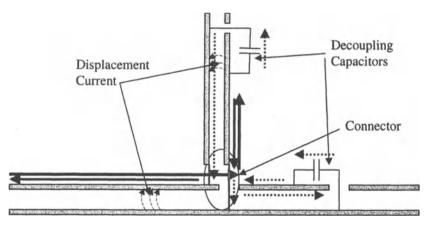

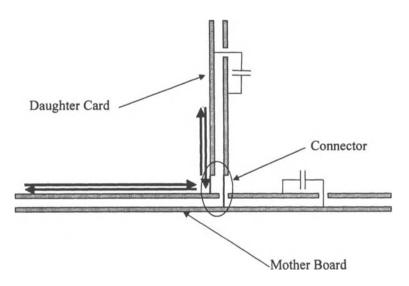

|   | 5.4 Motherboards and Daughter Cards          | 80  |

|   | 5.4.1 Connector Pin Assignments              | 82  |

|   | 5.5 Summary                                  | 83  |

| 6 | Controlling EMI Sources                      |     |

|   | – Intentional Signals                        | 85  |

|   | 6.1 Introduction                             | 85  |

|   | 6.2 Critical Signals                         | 86  |

|   | 6.3 Intentional Signals                      | 86  |

|   | 6.4 Intentional Signals – Loop-Mode          | 93  |

|   | 6.5 Controlling Emissions from Intentional   |     |

|   | Signals – Loop-Mode                          | 95  |

|   | 6.6 Intentional Signals – Common-mode        | 96  |

|   | 6.7 Intentional Signals – Common-mode        |     |

|   | with Interrupted Return Path                 | 99  |

|   | 6.7.1 Critical Signal Traces Crossing Splits | 99  |

|   | 6.7.2 Critical Signals Through Vias          | 100 |

|   | 6.8 Summary                                  | 102 |

| 7 | Controlling EMI Sources                      |     |

|   | – Unintentional Signals                      | 105 |

| 7.1 Introduction          | 105 |

|---------------------------|-----|

| 7.2 Unintentional Signals | 106 |

|                           |     |

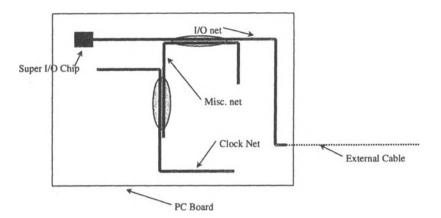

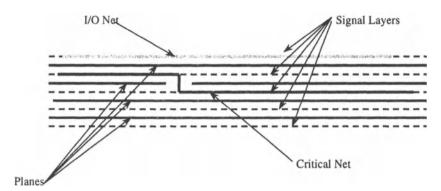

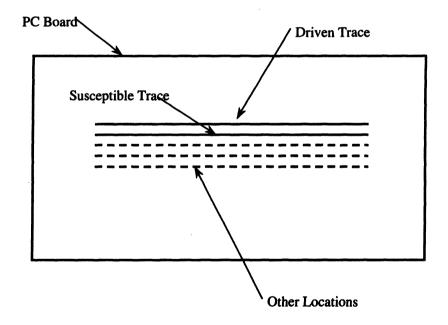

7.3 Unintentional Signals – Common-mode 106

| 7.4        | Controlling Emissions from Unintentional                     | 108 |

|------------|--------------------------------------------------------------|-----|

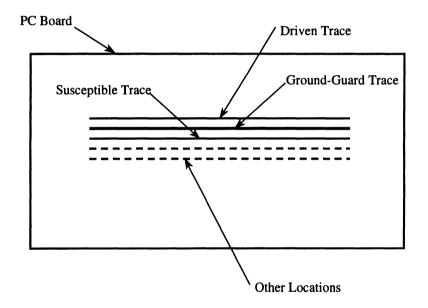

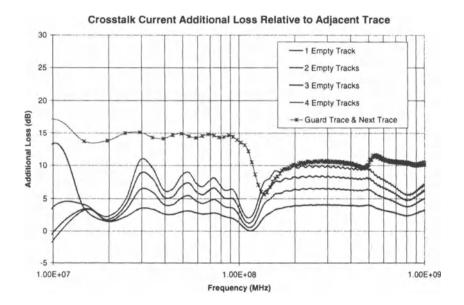

| 75         | Signals – Common-mode<br>Unintentional Signals – 'Crosstalk' | 108 |

| 1.5        | Coupling onto I/O Lines                                      | 113 |

| 7.6        | Controlling Emissions from Unintentional                     | 115 |

| 110        | Signals – 'Crosstalk' Coupling to I/O Lines                  | 115 |

| 7.7        | Summary                                                      | 118 |

| 8 De       | coupling Power/Ground Planes                                 | 121 |

| <b>9</b> 1 | Introduction                                                 | 121 |

|            |                                                              | 121 |

|            | Background<br>Calculating the Source of Decoupling Noise     | 122 |

| 0.5        | 8.3.1 Decoupling Noise from ASIC/ICs                         | 124 |

|            | power pins                                                   | 124 |

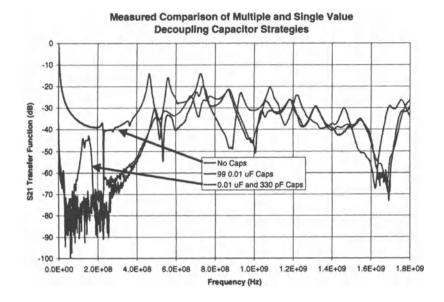

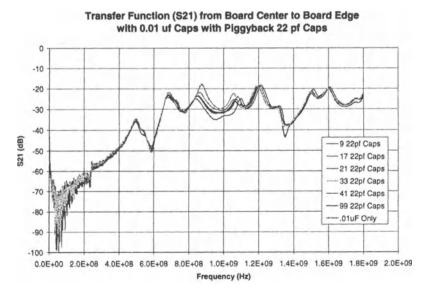

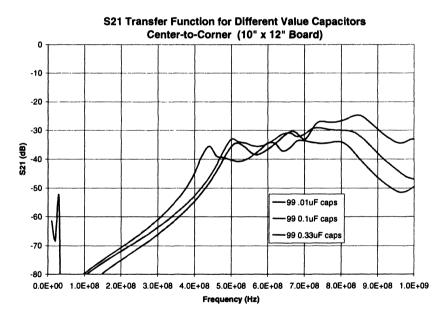

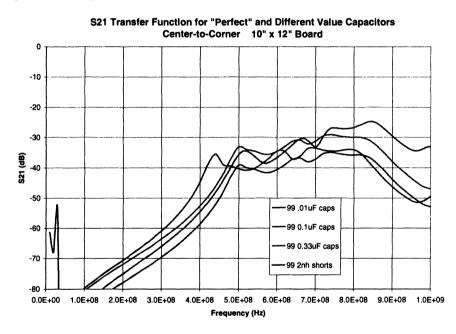

| 8.4        | Decoupling Capacitor Effectiveness                           | 130 |

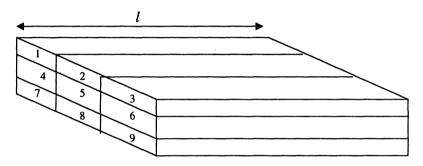

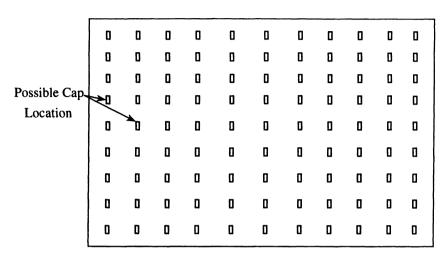

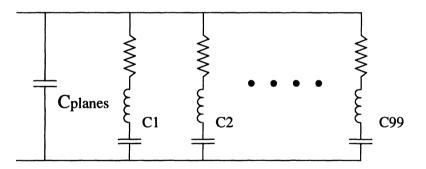

|            | 8.4.1 Test Board Description                                 | 131 |

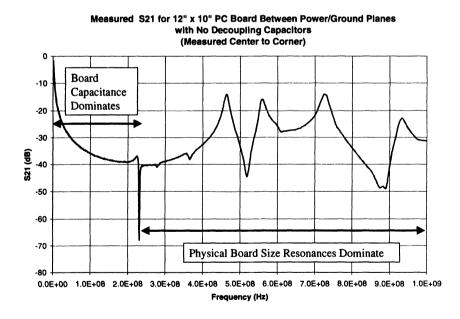

|            | 8.4.2 Empty Test Board Configuration                         | 134 |

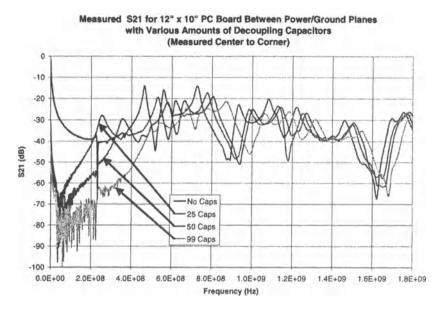

|            | 8.4.3 Quantity of Distributed (Global)                       |     |

|            | Decoupling Capacitors (.01uf Only)                           | 136 |

|            | 8.4.4 Quantity of Distributed Decoupling                     |     |

|            | Capacitors (0.01uf and 330 pF)                               | 137 |

|            | 8.4.5 Selecting the Value of the Decoupling                  |     |

|            | Capacitors                                                   | 140 |

|            | 8.4.6 Perfect Decoupling Capacitors                          | 140 |

|            | 8.4.7 Source Vs Distributed Decoupling                       | 141 |

|            | 8.4.8 Buried Capacitance Decoupling                          | 144 |

|            | 8.4.9 Lossy Capacitors                                       | 146 |

| 8.5        | Summary                                                      | 148 |

|            |                                                              |     |

## 9 EMC Filter Design

151

9.1 Introduction1519.2 Filter Design Concepts151

|    | 9.3 Filter Configurations                      | 155     |

|----|------------------------------------------------|---------|

|    | 9.3.1 Two-Component Filter                     |         |

|    | Configurations                                 | 155     |

|    | 9.3.2 Reference Connection for                 |         |

|    | Two-Component Filters                          | 157     |

|    | 9.3.3 Three Component Filter                   |         |

|    | Configurations                                 | 161     |

|    | 9.3.4 Single Component Filter                  |         |

|    | Configurations                                 | 163     |

|    | 9.4 Non-Ideal Components and the Impact on Fil | ters163 |

|    | 9.4.1 Non-Ideal Capacitors                     | 164     |

|    | 9.4.2 Non-Ideal Ferrite Beads                  | 166     |

|    | 9.4.3 Non-Ideal Zero Ohm Resistors             | 168     |

|    | 9.5 Common-Mode Filters                        | 168     |

|    | 9.6 Summary                                    | 169     |

| 10 | Using Signal Integrity Tools for EMC           |         |

|    | Analysis                                       | 171     |

|    | 10.1 Introduction                              | 171     |

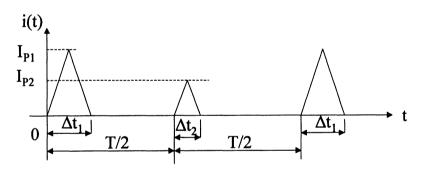

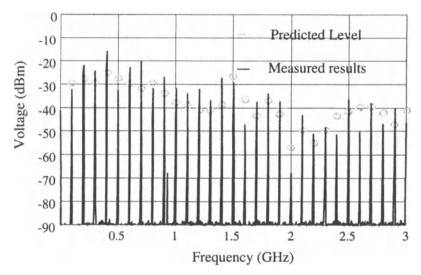

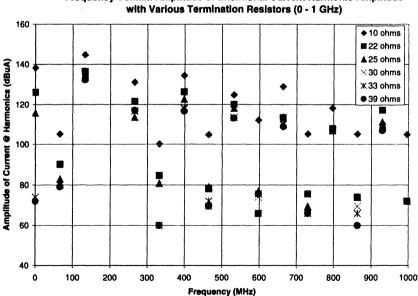

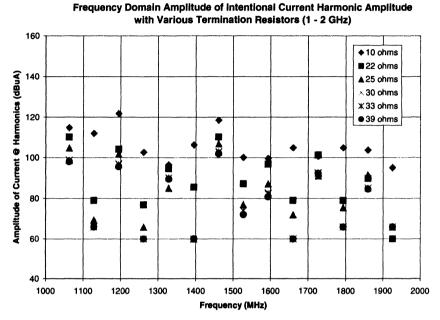

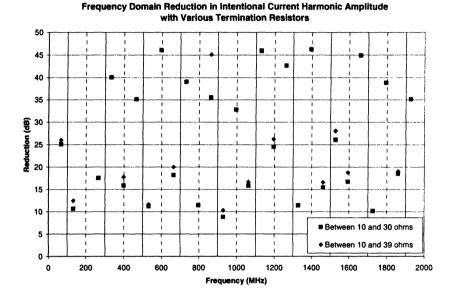

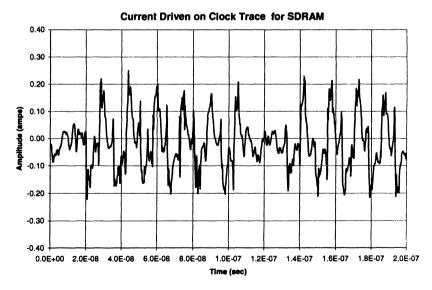

|    | 10.2 Intentional Current Spectrum              | 172     |

|    | 10.3 Trace Current for Decoupling Analysis     | 177     |

|    | 10.4 Differential Signals Analysis             | 179     |

|    | 10.4.1 Internal Differential Signal Lines      | 181     |

|    | 10.4.2 External I/O Differential Signal        |         |

|    | Lines                                          | 182     |

|    | 10.5 Crosstalk Analysis                        | 185     |

|    | 10.6 Summary                                   | 185     |

|    |                                                |         |

| 11 | <b>Printed Circuit Board Layout</b>            | 187 |

|----|------------------------------------------------|-----|

|    | 11.1 Introduction                              | 187 |

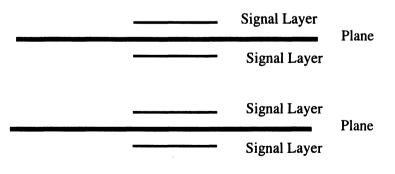

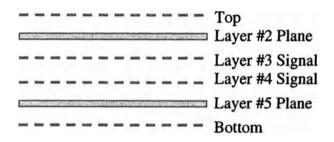

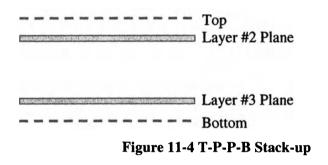

|    | 11.2 PC Board Stack-up                         | 187 |

|    | 11.2.1 Many Layer Boards                       | 188 |

|    | 11.2.2 Six-Layer Boards                        | 191 |

|    | 11.2.3 Four-Layer Boards                       | 192 |

|    | 11.2.4 One and Two-Layer Boards                | 193 |

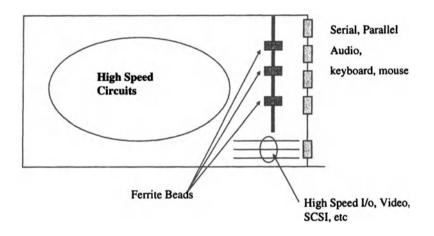

|    | 11.3 Component Placement                       | 195 |

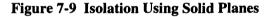

|    | 11.4 Isolation                                 | 195 |

|    | 11.5 Summary                                   | 196 |

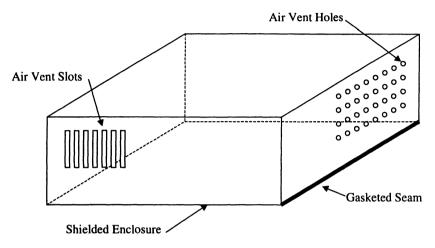

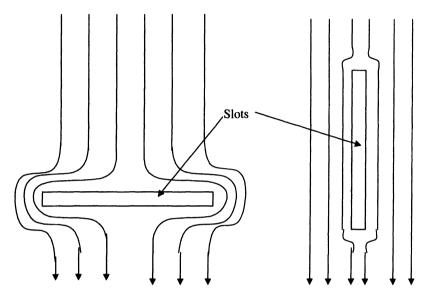

| 12 | Shielding in Enclosures with Apertures         | 199 |

|    | 12.1 Introduction                              | 199 |

|    | 12.2 Resonance Mode within Shielded Enclosures | 202 |

|    | 12.3 Shielded Enclosures                       | 208 |

|    | 12.3.1 Apertures and Openings                  | 208 |

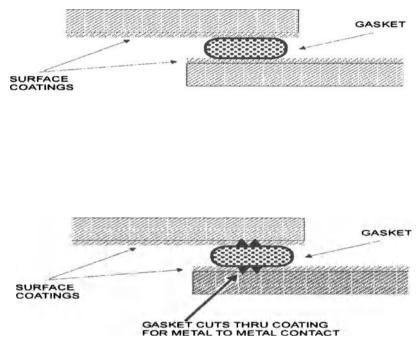

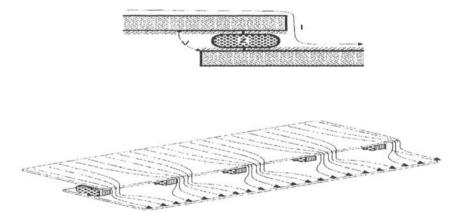

|    | 12.3.2 Gaskets                                 | 210 |

|    | 12.4 Predicting the Shielding Effectiveness    |     |

|    | of Enclosures with Apertures                   | 213 |

|    | 12.5 Shielding the PC Board Edge               | 215 |

|    | 12.6 Cable Shields                             | 216 |

|    | 12.7 Summary                                   | 218 |

| 13 | What To Do If a Product Fails                  |     |

|    | in the EMC Lab                                 | 221 |

|    | 13.1 Introduction                              | 221 |

|    | 13.2 Where Does the Signal Come From?          | 222 |

|    | 13.3 How Does the Signal Get Out               |     |

|    | of the Shielded Enclosure?                     | 223 |

|    | 13.3.1 Leaks through slots holes               |     |

|    | and apertures                                  | 223 |

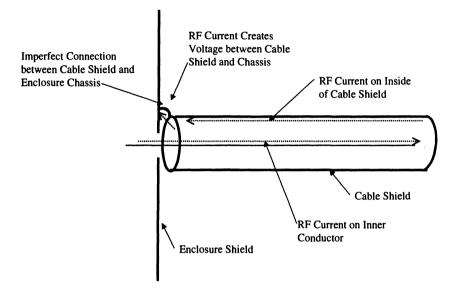

| 13.3.2 Conducted through the shield                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| on cables and wires                                                                                                                                                                                                                                                                                                                                                                                                              | 225                                                         |

| 13.3.3. Leaks from imperfect mating                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| of shielded cable shields to the                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

| enclosure                                                                                                                                                                                                                                                                                                                                                                                                                        | 226                                                         |

| 13.4 Coupling Mechanism                                                                                                                                                                                                                                                                                                                                                                                                          | 227                                                         |

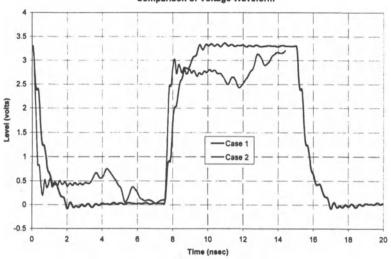

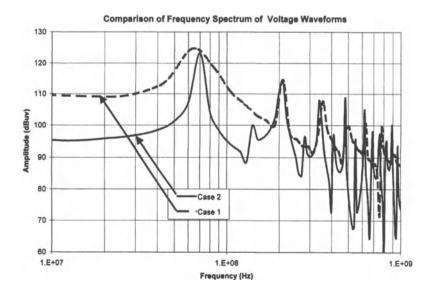

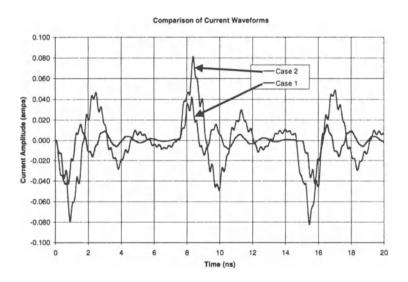

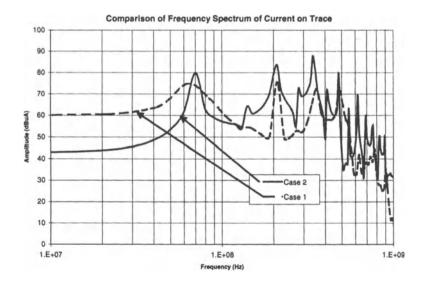

| 13.4.1 Case 1 Clock signal leaking                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

| from seam                                                                                                                                                                                                                                                                                                                                                                                                                        | 228                                                         |

| 13.4.2 Case 2 Clock signal leaking                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

| from an unshielded cable                                                                                                                                                                                                                                                                                                                                                                                                         | 228                                                         |

| 13.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                     | 229                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

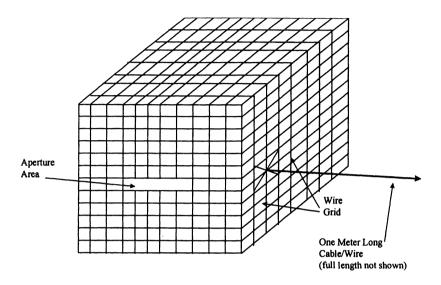

| Appendix A Introduction to EMI/EMC<br>Computational Modeling                                                                                                                                                                                                                                                                                                                                                                     | 231                                                         |

| Computational Modeling                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| Computational Modeling<br>A.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                       | 231                                                         |

| A.1 Introduction<br>A.2 Why Is EMI/EMC Modeling Important?                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

| Computational Modeling<br>A.1 Introduction<br>A.2 Why Is EMI/EMC Modeling Important?<br>A.3 EMI/EMC Modeling: State of the Art                                                                                                                                                                                                                                                                                                   | 231<br>232                                                  |

| Computational Modeling<br>A.1 Introduction<br>A.2 Why Is EMI/EMC Modeling Important?<br>A.3 EMI/EMC Modeling: State of the Art<br>A.4 Tool Box Approach                                                                                                                                                                                                                                                                          | 231<br>232<br>233                                           |

| Computational Modeling<br>A.1 Introduction<br>A.2 Why Is EMI/EMC Modeling Important?<br>A.3 EMI/EMC Modeling: State of the Art                                                                                                                                                                                                                                                                                                   | 231<br>232<br>233                                           |

| A.1 Introduction<br>A.2 Why Is EMI/EMC Modeling Important?<br>A.3 EMI/EMC Modeling: State of the Art<br>A.4 Tool Box Approach<br>A.5 Brief Description of EMI Modeling                                                                                                                                                                                                                                                           | 231<br>232<br>233<br>234                                    |

| <ul> <li>Computational Modeling</li> <li>A.1 Introduction</li> <li>A.2 Why Is EMI/EMC Modeling Important?</li> <li>A.3 EMI/EMC Modeling: State of the Art</li> <li>A.4 Tool Box Approach</li> <li>A.5 Brief Description of EMI Modeling<br/>Techniques</li> </ul>                                                                                                                                                                | 231<br>232<br>233<br>234<br>235                             |

| <ul> <li>Computational Modeling</li> <li>A.1 Introduction</li> <li>A.2 Why Is EMI/EMC Modeling Important?</li> <li>A.3 EMI/EMC Modeling: State of the Art</li> <li>A.4 Tool Box Approach</li> <li>A.5 Brief Description of EMI Modeling<br/>Techniques</li> <li>A.5.1 Finite Difference Time-Domain</li> </ul>                                                                                                                   | 231<br>232<br>233<br>234<br>235<br>235                      |

| <ul> <li>Computational Modeling</li> <li>A.1 Introduction</li> <li>A.2 Why Is EMI/EMC Modeling Important?</li> <li>A.3 EMI/EMC Modeling: State of the Art</li> <li>A.4 Tool Box Approach</li> <li>A.5 Brief Description of EMI Modeling<br/>Techniques</li> <li>A.5.1 Finite Difference Time-Domain</li> <li>A.5.2 Method of Moments</li> </ul>                                                                                  | 231<br>232<br>233<br>234<br>235<br>235<br>235<br>237        |

| <ul> <li>Computational Modeling</li> <li>A.1 Introduction</li> <li>A.2 Why Is EMI/EMC Modeling Important?</li> <li>A.3 EMI/EMC Modeling: State of the Art</li> <li>A.4 Tool Box Approach</li> <li>A.5 Brief Description of EMI Modeling<br/>Techniques</li> <li>A.5.1 Finite Difference Time-Domain</li> <li>A.5.2 Method of Moments</li> <li>A.5.3 Finite Element Method</li> </ul>                                             | 231<br>232<br>233<br>234<br>235<br>235<br>235<br>237        |

| <ul> <li>Computational Modeling</li> <li>A.1 Introduction</li> <li>A.2 Why Is EMI/EMC Modeling Important?</li> <li>A.3 EMI/EMC Modeling: State of the Art</li> <li>A.4 Tool Box Approach</li> <li>A.5 Brief Description of EMI Modeling<br/>Techniques</li> <li>A.5.1 Finite Difference Time-Domain</li> <li>A.5.2 Method of Moments</li> <li>A.5.3 Finite Element Method</li> <li>A.6 Other Uses for Electromagnetic</li> </ul> | 231<br>232<br>233<br>234<br>235<br>235<br>235<br>237<br>238 |

## Index

241

xiii

## Preface

Proper design of printed circuit boards can make the difference between a product passing emissions requirements during the first cycle or not. Traditional EMC design practices have been simply rule-based, that is, a list of rules-of-thumb are presented to the board designers to implement. When a particular rule-of-thumb is difficult to implement, it is often ignored. After the product is built, it will often fail emission requirements and various time consuming and costly add-ons are then required.

Proper EMC design does not require advanced degrees from universities, nor does it require strenuous mathematics. It *does* require a basic understanding of the underlying principles of the potential causes of EMC emissions. With this basic understanding, circuit board designers can make trade-off decisions during the design phase to ensure optimum EMC design. Consideration of these potential sources will allow the design to pass the emissions requirements the first time in the test laboratory.

A number of other books have been published on EMC. Most are general books on EMC and do not focus on printed circuit board design. This book is intended to help EMC engineers and design engineers understand the potential sources of emissions and how to reduce, control, or eliminate these sources. This book is intended to be a 'hands-on' book, that is, designers should be able to apply the concepts in this book directly to their designs in the real-world.

Chapter 1 provides an introduction into the basic concepts in this book, such as inductance, "ground", and shielding.

Chapter 2 continues the fundamentals of EMC with discussions on various coupling mechanisms, the frequency-domain harmonic content of time-domain signals, resonance phenomena, and potential emissions sources. Chapter 3 presents a brief introduction to inductance. While the subject of inductance could be an entire book by itself, this chapter presents an overview of self-inductance, mutual-inductance, and partial-inductance. A number of basic formulas are included to find the inductance for simple loop geometries.

Chapter 4 discusses the concept of "ground". There are a number of different meanings for the term "ground", causing this term to be often misused and misunderstood. These different meanings are discussed, and issues with the various purposes of "ground" highlighted.

The next three chapters are the heart of the basic concept of controlling the currents on the printed circuit board. Chapter 5 discusses return current design, and the paths the return current must often take (if proper design practices are not followed). Chapter 6 identifies the potential sources from *intentional signals*, while Chapter 7 identifies the potential sources from *unintentional signals* on the printed circuit board. Both types of signals must be considered in order to properly control the currents on a printed circuit board.

Chapter 8 discusses decoupling power and ground-reference planes on printed circuit boards. This is an area where many myths, misinformation, and unfounded beliefs exist among designers. Chapter 8 also presents the two main sources of EMI 'noise' between the planes, and discusses various decoupling capacitor strategies' effectiveness in reducing this noise.

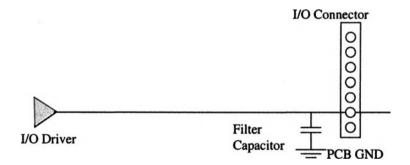

Chapter 9 presents basic filter concepts for I/O areas on printed circuit boards. The I/O filter is usually the last defense against signals from inside a metal enclosure from being coupled onto the outside cables and causing emissions. Careful design of the I/O filter, and proper connection of the filter capacitor to the appropriate reference, can change an ineffective filter to an effective filter.

Chapter 10 discusses how to use standard signal integrity tools for EMC applications. These tools are usually used by design engineers to ensure functionality of the various high-speed traces on the printed circuit board, and can often help analyze the EMC effectiveness of various design options.

Chapter 11 discusses the printed circuit board stack-up for various board configurations. Careful selection of which routing

layer is used for which signals can make a significant difference to the return current path, and ultimately, to the EMC emissions.

Chapter 12 presents an introduction to shielding for printed circuit boards. Resonance effects within the enclosure, the effect of aperture size, and gasket design can all affect the overall shielding and ultimately, the amount of emissions 'leaking' from the enclosure.

Finally, Chapter 13 discusses a strategy to help quickly identify the source of any signals which may cause EMC emissions levels that are over the allowed limit in the EMC test chamber. Random application of copper tape, ferrite beads, and capacitors is not the optimum way to solve emissions problems quickly. The source of the emission should be identified and the 'fix' applied to the source, for the most effective and efficient solution.

The author encourages all readers to not blindly accept rules-ofthumb from so-called experts. It is important to understand the basic concepts for the important issues, and to make the correct decisions for each issue independantly. This does not mean the 'experts' are not correct, because they often *are* correct. This means that you should understand "why" or "why not" to implement a specific design practice, and to use engineering judgement for each circumstance. Design rules-of-thumb are correct for certain circumstances, but ultimately <u>you</u> need to make sure they apply to your specific circumstance.

## Acknowledgements

The author wishes to gratefully acknowledge the editorial and technical review by Michelle Cook of IBM in Austin, Texas. Her EMC engineering background and editorial skills provided a valuable combination that enhanced the quality of this book. Her repeated reviews of the various revisions of the book helped make this book a success. Recognition, acknowledgement and gratitude is also due to my wife. Susan Archambeault. Her editorial reviews and attention to detail throughout the manuscript enhanced the professional appearance and general readability of the book. Her patience during the writing of this book during the author's mood swings of desperation, exuberance, and despair is greatly appreciated! The author also wishes to acknowledge the technical review from Vince Lisica of IBM in Research Triangle Park, NC. His early review and comments helped fashion the overall content of the book.

Finally, the author wishes to gratefully acknowledge the contributions made by Professor James Drewniak at the University of Missouri-Rolla. His advice helped shape the outline of the book, and his detailed technical review helped ensure that the concepts were clear, correct, and easy to understand. He has been a good friend throughout the writing of this book and made significant contributions in a number of ways to the final manuscript.

## **Chapter 1**

# Introduction to EMI/EMC Design for Printed Circuit Boards

#### **1.1 Introduction to EMI/EMC**

Electromagnetic Interference and Electromagnetic Compatibility (EMI/EMC) first became a concern in the 1940's and 1950's, mostly as motor noise that was conducted over power lines and into sensitive equipment. During this period, and through the 1960s, EMI/EMC was primarily of interest to the military to ensure electromagnetic compatibility. In a few notable accidents, radar emissions caused inadvertent weapons release, or EMI caused navigation systems failure, so military EMI/EMC was concerned chiefly with electromagnetic compatibility, especially within a weapons system of a airplane or ship.

With the computer proliferation during the 1970s and 1980s, interference from computing devices became a significant problem to broadcast television and radio reception, as well as emergency services radio reception. The U.S. government decided to regulate the amount of electromagnetic emissions from products in this industry. The Federal Communications Commission (FCC) created a set of rules to govern the amount of emissions from any type of computing device and how those emissions were to be measured. Similarly, European and other governments began to limit emissions from computing devices. During this time, EMI/EMC control was limited to computers, peripherals, and computer communications products.

During the 1990's, the concern over EMI/EMC has been found to broaden dramatically; in fact, many countries have instituted import controls requiring that EMI/EMC regulations be met before products

can be imported into that country. The compatibility of all devices and equipment must coexist harmoniously in the overall electromagnetic environment. Emissions, susceptibility to emissions from other equipment, susceptibility to electrostatic discharge – all from either radiated or conducted media – are controlled. No longer is this control limited to only computers. Now any product that may potentially radiate (or conduct on cables) EMI, or that could be susceptible to other emissions (or noise conducted into the product), must be carefully tested. Products with no previous need for EMI/EMC control must now comply with the regulations, including dishwashers, video cassette recorders (VCRs), industrial equipment, and most electronic equipment.

While commercial products have come under tighter control for EMI/EMC, the military has not relaxed its EMI/EMC requirements. In fact, because of the higher degree of automation and faster processing speeds, military EMI/EMC control has become a significant part of all military programs.

EMI/EMC design means different things to different people. The standards for commercial applications, such as VCRs, personal computers, and televisions are fairly loose compared to the military/TEMPEST<sup>1</sup> standards, however, they are still difficult to meet. The result of the relaxed nature of these commercial standards is that designers are constantly caught between lowering emissions and susceptibility while meeting cost reduction goals. The trade-offs between EMI/EMC design features are clear, but whether the absolute need for one or another individual EMI/EMC component is required is not so clear. Traditionally, EMI/EMC engineers have used experience, as well as equations and graphs from handbooks, frequently taken out of context, to help during the product design phase. Very little high quality EMI/EMC engineering-level training is available at universities, or at any institutions, and most engineers working in this area find these traditional methods somewhat inadequate.

Military, space, and other government applications must control the emissions of electronics for security, weapon systems functionality, or proper communications, most often to a level far below the commercial emissions/susceptibility level. This increased

<sup>&</sup>lt;sup>1</sup> TEMPEST is the U.S. government code name for the project which controls data related RF emissions from equipment processing classified information.

control requires additional EMI/EMC design features, and greater expense, just when these applications are being forced to reduce costs.

EMI/EMC problems are caused by changes in current with respect to time on conductors within the equipment, known as *di/dt* noise. This current change causes electromagnetic emissions. Alternatively, external electromagnetic energy can induce *di/dt* noise in circuits, causing false logic switching and improper operation of devices. Most high speed fast rise time signals cause EMI/EMC problems. These problems are magnified through the wires and cables attached to the product, creating more efficient antennas at lower frequencies. The typical solution is to use metal shielding, to filter all data/power lines, and to provide significant on-board filtering of signal lines and power planes. The real question is "How much is enough?" and "How much is too much?".

While many EMC engineers have long advocated close attention to EMC design early in the product design cycle, this 'close attention' often was simply a long list of "do's" and "don'ts" in the form of EMC design rules. These rules were most often based on past experience on some specific product or product family, and often these rules contradicted each other. The absence of true, root cause analysis yielded no real understanding of *why* a certain rule was required, or, even more importantly, when a particular rule could not easily be followed (due to some design constraint), then what *alternatives* should be investigated. The designers were simply told "do this or else".

This resulted in a typical design process as follows:

1. EMC engineer provides product designers with list of EMC design rules.

2. Product designers are unable, or unwilling, to implement all the EMC design rules.

3. The product is designed/built including only convenient EMC design rules.

4. Once prototype product is tested in the EMC test chamber, it fails.

5. EMC engineer and design engineer spend 2 weeks to 2 months adding capacitors, ferrite beads, gasket, and finger stock until problem is solved.

6. Product design is updated with EMC 'fixes', and general manufacturing begins.

This design process resulted in delayed first customer shipments of products as well as increased product cost, since the EMC parts were not designed into the product initially. Clearly, this is not a desirable design process, but it is very common!

The goal of this book is to try to remove the magic from the EMC design process. Many have referred to EMC design as black magic, voodoo, simply wild guesses, and worse. EMC design is complex. There are many interconnected events that occur, and most are hard to predict, especially when taken together. If each potential EMC emissions source is taken individually, and proper design approaches can be applied to address each potential source, however, the designer will not get confused while looking at the overall product.

The authors believe that the goal of every design project should be to pass the EMC requirements the *first time* in the EMC test chamber. If a particular IC has more EMI noise than expected and causes a failure, this should be the exception, and not the rule, and the problem should be easily corrected.

Proper EMC design is not just a list of rules. It does require a thought process that considers the potential sources and addresses each in turn. Naturally, the primary goal is to insure the product functions as intended. If, however, during the design phase, these EMC considerations are included and matched to the functionality requirements, then designers can achieve success in both areas with the first design pass.

#### **1.2 EMI Emissions Sources**

The most efficient way to reduce EMI emissions is to control the contributing signals at their source. So, where do these signals originate? There are a number of places where these signals can originate, but the majority of the signals start as fast switching currents in ICs.

Nearly all EMI emissions come from common-mode currents that exist someplace within the product. All of these common mode currents come from some intentional current, that is, some current in an IC that is needed for the functionality of the product. If the intentional signal is controlled to only include the harmonics that are necessary for the proper operation of the product, then the chance of a high-frequency harmonic causing unwanted emissions is greatly reduced.

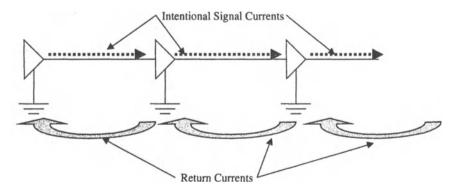

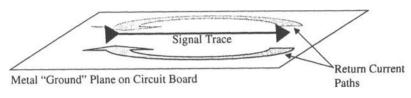

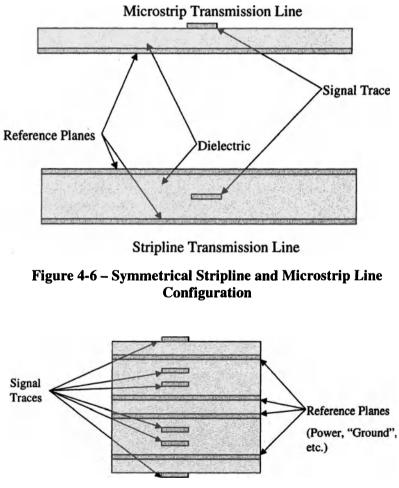

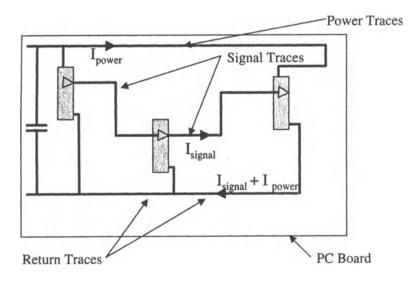

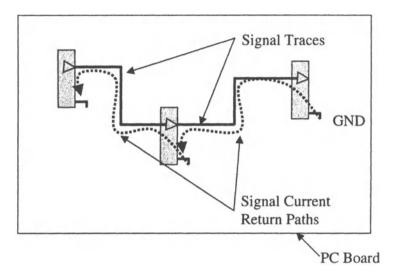

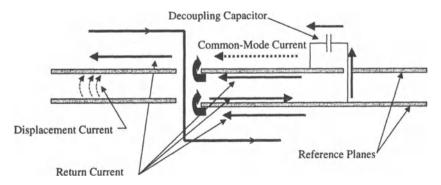

The source of these common mode currents is most likely the intentional signal return current path. While printed circuit board (PCB) layout engineers will take great care to route a trace from source to destination (driver to receiver), very little attention, if any, is given to the return current path. When clock speeds were less than 10 MHz or so, the return current path was not particularly important. Today, on-board clock speeds of 200 - 400 MHz, and data bus speeds above 1 GHz are common, therefore, the signal trace must be considered a microwave transmission line. The return current path at high frequencies is critical, both to the EMC performance and the functionality performance of the signal trace.

#### 1.3 Inductance

One of the most commonly misunderstood concepts is the concept of inductance. Beginning engineering students learn about inductance as specific components in inductors and transformers, but seldom consider the inductance of the current paths in our ground-reference planes, traces, etc. Inductance requires a current flowing through a loop. Sometimes the total path is not clear, and total path may even be partially radiated, so the concept of partial inductance is also important. Partial inductance can be combined to create the total loop inductance. However, if the partial inductance of a portion of the path is considered and reduced, then the total inductance of the path is also reduced.

The high speed signal rates used today make the consideration of loop inductance and partial inductance more important than ever before. Even a perfect superconductor has inductance. The impedance of this inductance provides a voltage potential when a current flows through it. This voltage potential causes noise across

ground-reference planes, signal amplitude drop, and adds to EMI emissions.

#### 1.4 "Ground"

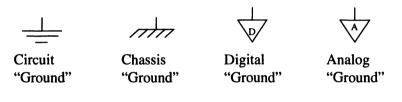

If inductance is one of the most commonly misunderstood concepts, "ground" is the MOST misunderstood. When the term "ground" is used, designers mean a variety of different things. It might mean the safety earth reference for the 50/60 Hz AC power. It might mean the signal reference for a high speed trace. It might mean the power return on a PCB, or, it could mean the chassis reference for a shielded chassis. It might even mean the actual earth ground, as in the ground plane at an Open Area Test Site (OATS), where EMI emissions are often measured.

It is clear that it is impossible for all these different uses of the word "ground" to be at the same electric potential, but that is really the intended definition of "ground". "Ground" is the point of zero potential. Actually, "ground" or zero potential only exists at infinity, and so, unless some really long leads are used, true zero ground potential will not exist in our products.

A much more clear and accurate way to describe the various uses of "ground" would be to use the terms: earth-ground, groundreference, power-reference, chassis-reference, etc. Then both the listener and the speaker are more likely to clearly understand each other.

#### 1.5 Shielding

Another area of confusion in EMC is the concept of shielding. Classical shielding theory shows the effect of a plane wave hitting a shield with an aperture. With the density of our products, designers seldom have a plane wave hitting our apertures in a shield, so this classical approach can be misleading.

Within typical products, the source of the energy is closely coupled to the enclosure shield and apertures. This close capacitive, inductive, or electromagnetic coupling induces currents on the shield. The spacing of the shield to the source is important and can cause the coupling to change dramatically. Any currents induced in the shield can find apertures and transfer energy outside for the enclosure.

#### 1.6 Summary

The most efficient way to approach proper EMC design for PCBs is to consider the various sources and control the signals at their sources. Further chapters will provide much more detail about the different sources and how to control each of the individual sources. EMC must be considered early during the design phase, and indeed, throughout the entire design phase.

It is important not to treat EMC design as simply following a cookbook. During the design, there must be a number of engineering trade-offs. If the designer understands the goals, and understands where the sources of EMI emissions occur and how to control them, then the designer will be successful in making the correct design trade-off. If the EMC design process is to just follow a set of rules, then when these rules become difficult or impossible to implement, they will be ignored, the product will likely fail, and the 'typical' design process explained earlier will repeat itself.

In order to completely understand the thought processes associated with the sources, etc, some basic concepts must also be clearly understood, such as "ground", inductance, and shielding. There are many misconceptions in these areas, and this book is intended to help reduce the confusion about them.

## **Chapter 2**

## **EMC** Fundamentals

#### 2.1 Introduction

The most fundamental fact about EMC is that it is NOT magic, witchcraft, or divine intervention. It is about current flow, electric field and magnetic field coupling, and electromagnetic radiation. The interactions between all the individual system components are often complex and hard to visualize simultaneously. In order to properly understand the various issues, the overall complex problem must be broken into smaller, discrete problems that can be more easily understood. Straightforward scientific and engineering principles can then be applied with success.

This chapter will introduce some basic concepts that are fundamental to EMC problems. A good basic understanding of these fundamentals is necessary before the overall complex problem can be broken into isolated individual problems and solved properly. It is common practice by some EMC engineers to use the 'try-it-andsee' approach. That is, very little consideration is given to root cause analysis (as if the laws of physics might be somehow different for this product). When the product fails EMC requirements, they will try a capacitor here, or a ferrite bead there, or more gasket in another place. Eventually, some combination of things will work together, and the product will pass the EMC requirements. Another approach is the 'shot gun' approach. With this approach, the design engineer includes every possible filter and shielding design options with the hope that something will work. Either of these approaches increase the cost of the product and is a far from optimum design practice.

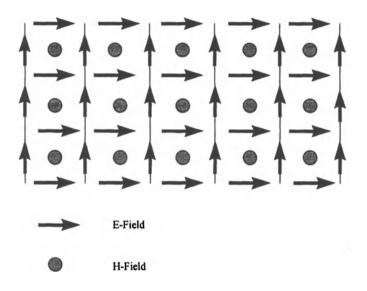

#### 2.2 Coupling Mechanisms

The two fundamental coupling mechanisms are electric field coupling and magnetic field coupling. The coupling from the noise source to the ultimate radiator could be either electric or magnetic filed coupling or it could be a combination of both. Understanding these coupling mechanisms, and how they might manifest themselves in a product design, is an important part in controlling them.

#### 2.2.1 Electric Field Coupling

Electric field coupling is due to displacement current through a capacitive effect. That is, we do not intend the current to flow in this particular direction, but the natural parasitic capacitance provides a lower impedance path to the current than the intended path provides. Current must always flow in a complete loop, so the loop impedance is the important factor.

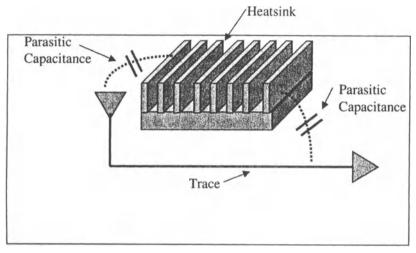

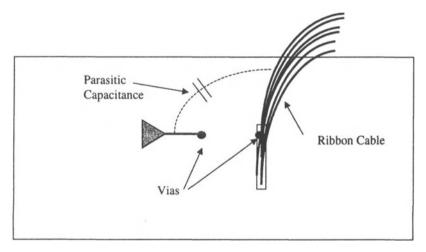

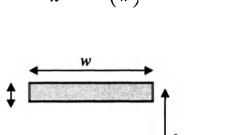

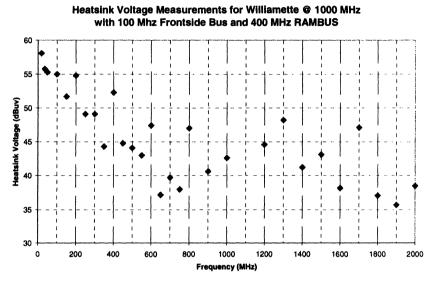

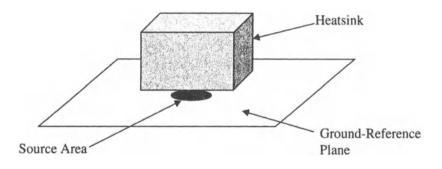

For example, Figure 2-1 shows a typical printed circuit (PC) board with a few components on it. A clock buffer drives a trace that passes near a large ASIC/IC with a heatsink above it. As the trace passes the heatsink, there is a parasitic capacitance between the trace and the heatsink. There is also a parasitic capacitance between the heatsink and the clock buffer. (Naturally, there is also parasitic capacitances between the heatsink and the receiver, the shielded enclosure, and all other parts of the system, but for this example, they are small enough to not affect the EMC performance.) The impedance of a capacitor is given by

$$X_c = j \frac{1}{2\pi fC} \tag{2.1}$$

where C = capacitance, and f = frequency.

#### EMC Fundamentals / 11

Figure 2-1 PC Board With Components

The amount of capacitance is set by the physical geometry. The impedance, however, will be affected by frequency. Higher frequency harmonics will encounter lower impedance for a given geometry.

Recall that all current must flow in a complete loop back to its source. The intended path in this example is to have the current at all harmonic frequencies leave the clock buffer, travel through the trace to the receiver, and then return to the clock buffer through the ground-reference plane. In this example, however, the parasitic capacitances between the trace and heatsink, and between the heatsink and the clock buffer, provide a lower impedance path than the intended one, causing at least some of the current to flow through the heatsink. While we might not initially care about this return current path, we should recognize that the heatsink is a physically larger radiator than the trace. The heatsink is very likely to be a more efficient radiator, especially at high-frequency harmonics, and can cause emissions that were unnecessary and must be contained by improved shielding.

#### 2.2.2 Magnetic Field Coupling

Magnetic field coupling is due to conduction current through an inductive effect. In this case, we do intend the current to flow in a particular direction, but the natural parasitic inductance provides a lower impedance path to the current than the intended path provides. Since current must always flow in a complete loop, the loop impedance is again the important factor.

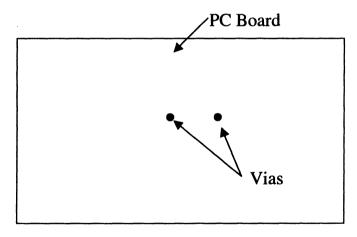

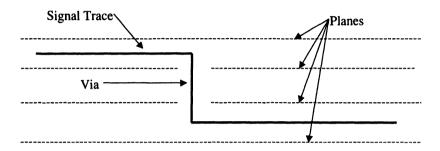

For example, Figure 2-2a shows a view of two PC board vias that are between two solid planes (such as a power and groundreference planes). In this example, the same clock buffer from the previous example is used, only this time, the trace is buried between various layers (as shown in Figure 2-2b) to avoid the electric field coupling described in the previous example. The trace usually must change layers at some point (to avoid other traces and devices), and the signal current travels on the via shown in Figure 2-2b.

Figure 2-2a PC Board with Vias Example

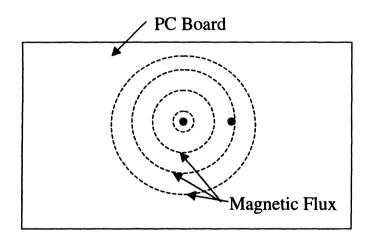

In this example, the second via is connected to an internal unshielded cable, such as a ribbon cable for a disk drive. The current in the first via causes magnetic flux lines, some of which will intersect the second via, as shown in Figure 2-2c. These magnetic flux lines will induce a current in the second via which will be conducted onto the ribbon cable. This parasitic mutual inductance will have a lower impedance for the higher harmonic frequencies, and will more easily conduct current away from its intentional path and onto potentially harmful unintentional paths (as described in Chapters 6 and 7).

Figure 2-2b PC Board with Vias Example (Inside View)

Figure 2-2c PC Board with Vias Example with Magnetic Flux

Recall that all current must flow in a closed loop back to its source. If we suppose the internal ribbon cable has a sufficient parasitic capacitance between the cable and the original clock buffer, then at least some of the current might flow through this path as

shown in Figure 2-2d. The combination of the parasitic mutual inductance and parasitic capacitance causes current to flow in the unshielded cable, and radiate onto the structure of the shielded enclosure. This requires the shielded enclosure to have additional shielding, again increasing the cost and complexity of the enclosure.

Figure 2-2d Example of Parasitic Return Current Path

#### 2.3 Signal Spectra

The harmonic spectra of the intended signals are a very important EMC design consideration. The fundamental harmonic frequency is seldom the problem frequency. Most EMC problems are from higher frequency harmonics.

#### 2.3.1 Clock Signals' Harmonic Frequencies

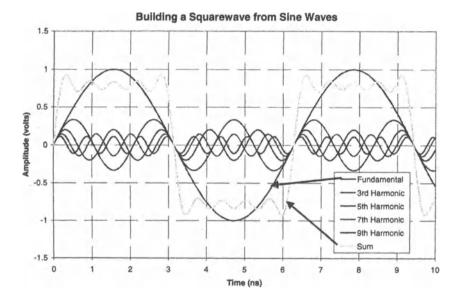

From a Fourier analysis, the harmonic frequency content from a simple square wave consists of the fundamental frequency and all the odd harmonics. The amplitude of the individual harmonic frequency is given by

$$A_n = \frac{1}{n} \tag{2.2}$$

where n = odd numbered harmonic (1, 3, 5, 7, ...), and  $A_n = \text{amplitude of harmonic.}$

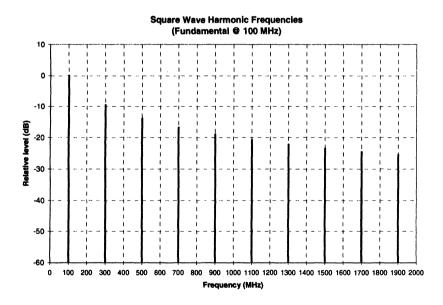

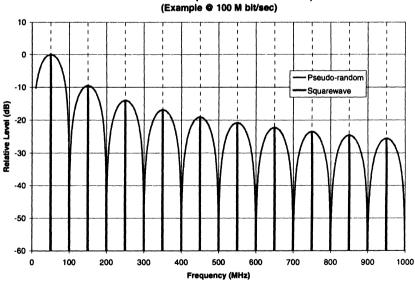

Figure 2-3 shows an example for a 100 MHz square wave. The amplitude is displayed in dB, and it is apparent that the amplitude of the higher frequency harmonics does not decay fast.

This example had no even harmonics because the duty cycle was exactly 50% and the square wave has equal rise and fall times. This is seldom the case in the real world. A slight change in duty cycle will create significant even harmonic amplitude. Even if the duty cycle is exactly 50%, a difference in the rise and fall time will create even numbered harmonics.

Figure 2-3 Example of Harmonic Content for 100 MHz Squarewave (or 200 Mb/s Squarewave)

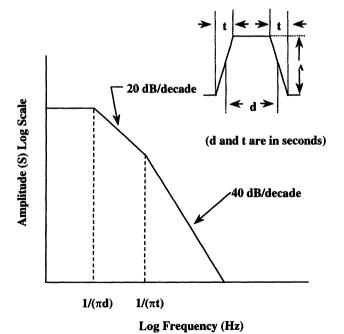

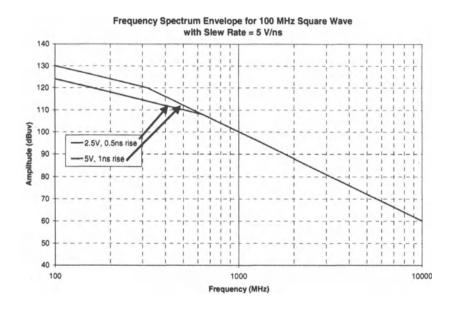

The previous example does not include the effect of rise/fall time for the pulse. In fact, the previous example used both rise and fall times of zero. When the real rise and fall times are included, the higher frequency harmonics are affected. Figure 2-4 shows the envelope of the frequency spectrum of a typical trapezoidal pulse based on the pulse width and the rise and fall times of the pulse. Since higher frequencies tend to radiate more efficiently from traces, etc. and are also able to radiate through smaller openings in the metal enclosure, it is best to keep high-frequency harmonics as low as possible. As Figure 2-4 shows, the amplitude of the pulse spectrum decreases with higher frequency. The spectrum decreases at a rate of 20 dB per decade of frequency above a frequency related to the pulse width, and at 40 dB per decade above a frequency related to the pulse rise/fall time. The slower the rise/fall time, the lower frequency at which the second break occurs, resulting in reduced signal levels at high frequencies. Clearly, the slower the rise and fall times of a pulse, the lower the potential frequency domain harmonic content of that signal.

Figure 2-4 Envelope of Spectrum of Trapezoidal Pulse

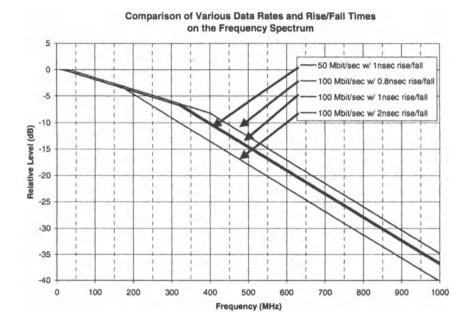

#### 2.3.2 Hertz vs. Bits-per-Second

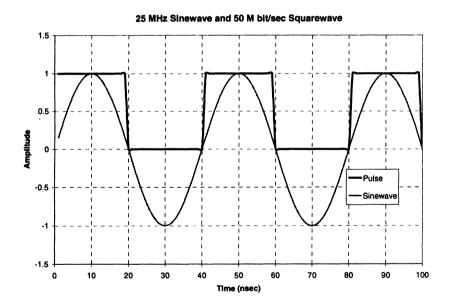

There is confusion sometimes about the difference between a (for example) 50 M bit/sec signal and a 50 MHz signal. These are not the same thing, and the fundamental frequency of the 50 M bit/sec signal is not 50 MHz. Figure 2-5 shows an example of a 50 M bit/sec square wave and the fundamental sinewave at 25 MHz. In effect, the squarewave data rate only uses one bit width (which is one half of the full sinewave cycle) to determine the data rate. This means that a 100 M bit/sec pulse will have its odd numbered harmonics at 50 MHz, 150 MHz, 250 MHz, 350 MHz, etc.

Figure 2-5 Comparison of 25 MHz Sinewave and 50 Mbit/sec Squarewave

#### 2.3.3 Non-Squarewave Data Signals

Clock signals are typically a square wave, but data and address signals change from moment to moment. The instantaneous spectrum will change with the data as well. The basic harmonic content is similar to the square wave and based on a sinc type function<sup>1</sup>. If a max-hold function is applied to the changing spectrum from a pseudo-random bit stream, an envelope develops as shown in Figure 2-6. The peaks of the harmonic envelope are centered on the squarewave harmonics. At any instant in time, however, the actual harmonic frequency and amplitude will be under the envelope and probably not at the squarewave harmonic.

As mentioned in a previous section, if the duty cycle is not exactly 50%, then the null frequencies in Figure 2-6 will have some non-zero values, depending on the amount of deviation form the 50% duty cycle.

Pseudo-Random and Square Wave Harmonic Frequencies (Example @ 100 M bit/sec)

Figure 2-6 Envelope of Spectrum for Pseudo-Random Bit Stream

<sup>&</sup>lt;sup>1</sup> The sinc function is a sin(x)/x function.

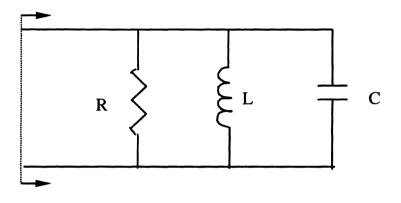

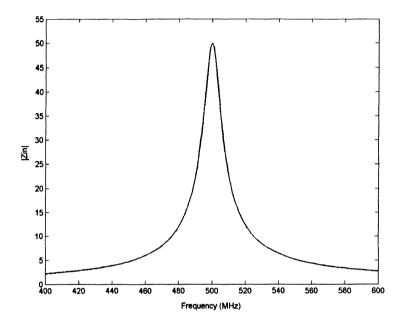

#### 2.4 Resonance Effects

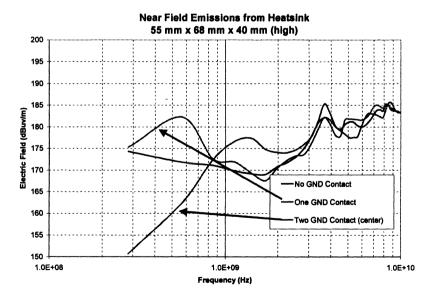

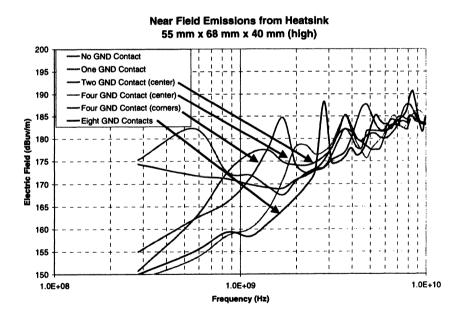

Most EMI emissions are not broad band but fairly narrow band. A resonance is excited somewhere in the system. It may be a resonance of an external cable is excited and becomes an efficient radiator, or an internal heatsink is excited and becomes a good radiator, or any number of other things that can become efficient radiators at specific frequencies if excited.

Resonance is either a physical size phenomenon or a circuit based phenomenon. Circuit based resonances are due to capacitive and inductive reactive impedance components being equal and opposite phase. Energy is stored in the capacitor and then in the inductor, repeatedly.

Physical resonance is due to the physical size of the conductor. For example, a wire in free space, when excited at its center, behaves like a dipole antenna. This 'antenna' is an antenna whether or not we intended it to be one! The antenna will be excited most effectively when the size of the wire is one-half the wavelength of the exciting frequency. The physical length of the antenna determines the resonance frequencies. Typically, a straight wire will be resonant at odd numbered half wavelength harmonics.

Resonances can increase the amount of emissions because the final radiator is more efficient. For example, a personal computer product had a front panel LED display. The LEDs needed to be visible to operators and were on the outside of the metal enclosure. By themselves, the LEDs and their associated circuitry were not an efficient radiator at the frequencies (and the harmonics) contained in the circuits. A plastic door was positioned near the LED display This plastic door was not part of the metal enclosure and area. considered not an EMC concern. However, the plastic door latch was built on a metal rod that was about 30 cm long. Even though the metal latch rod was not in physical contact with the LED circuits, the parasitic capacitance and inductance coupled energy onto it, and harmonic signals in the 500 – 600 MHz range from the LED circuits were radiated efficiently! The halfwave resonant frequency for a 30 cm long 'wire' is about 500 MHz, so the metal latch rod was an efficient antenna for harmonics around this frequency. This was an

example of where an unexpected resonance increased the emissions significantly.

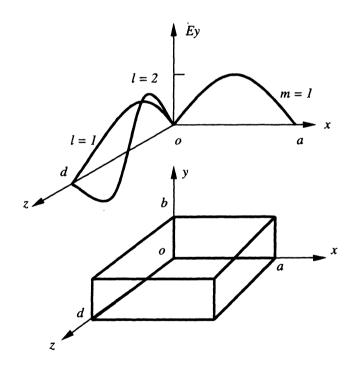

Cavity resonances are based on the volume of the enclosure/cavity. Boundary conditions force the tangential electric field to be zero on a perfectly conducting metal wall. In an empty rectangular cavity, whenever the cavity size allows an integer number of half wavelengths along any dimension, it will support standing (or stationary) waves, and is resonant. For an empty rectangular cavity, the frequencies where the cavity is resonant is given in [2.1] by

$$f_{mnp} = \frac{1}{2\sqrt{\varepsilon\mu}} \sqrt{\left(\frac{m}{a}\right)^2 + \left(\frac{n}{b}\right)^2 + \left(\frac{p}{c}\right)^2}$$

(2.3)

where:

a, b, and c = length of the sides of the cavity, and m, n, and p = integer numbers (only one can be zero at a time).

Equation (2.3) only applies to empty rectangular cavities. Typically, electronic or computer products contain a number of circuit boards, internal cables, power supplies, etc. Each of these objects alter the boundary conditions and therefore change the resonant frequencies. In an enclosure with little open space, there is little space to support the standing waves, and the likelihood of internal cavity resonances is low.

#### 2.4.1 Magic and Luck

One of the main reasons that EMC has a reputation for being magical is because of the effects of resonance. These are not generally from straightforward wire or cavity resonances, but because of the interaction between the physical resonances and the circuit based resonances when the parasitic elements are included. As mentioned earlier, the parasitic elements are difficult or impossible to compute with simple closed form equations, and so they are often ignored, but they exist whether they are ignored or not.

For example, in the past, a common design practice was to intentionally not connect the PC board ground-reference plane directly to the metal chassis at all of the PC board mounting screw locations. Often circuit pads were left on the PC board so that one could later install a capacitor, zero-ohm resistor, or ferrite bead as testing required if problems occurred. Unfortunately, this created more problems than it solved since even the zero-ohm resistor adds inductance (impedance) and is a poor connection at high frequencies.

Traditionally, engineers would try different values of capacitor, ferrite, etc. until the emissions were low enough to pass the requirements. Often, while trying various combinations of components, they would observe the signal of interest reduced, but another frequency signal unexpectedly raised above the limits! Unknowingly, they were simply tuning the resonances of the various parasitic elements with their added circuit elements until they were lucky enough to arrive at a combination that allowed the resonances to add or subtract in their favor.

Obviously, this is not the preferred approach. Rather than depend on luck and many hours spent in the EMC laboratory trying various circuit combinations, up front design and consideration of the parasitic circuit elements, the possible resonances, and the overall equivalent circuits will help the designer be successful the first time.

# **2.5 Potential Emissions Sources**

To understand the potential emissions sources in the EMC test chamber, the product under consideration should be enclosed in an imaginary enclosure. Any thing that leaves this imaginary enclosure is a possible emissions source.

# 2.5.1 Shielded Products

There are two ways for noise energy to escape the shielded enclosure. Energy can escape through openings in the metal enclosure or be conducted through the enclosure on I/O cables and wires.

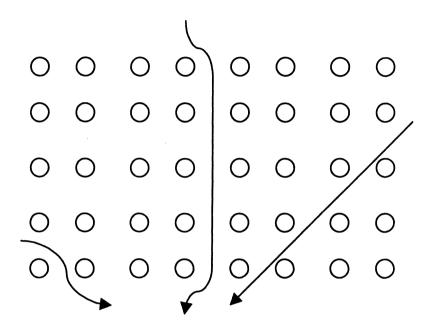

Openings in the enclosure are typically air vent areas, seams where metal enclosure parts are joined, and any other doors and windows. Noise energy escapes these openings and causes RF

current on the outside of the enclosure, cables, etc. in a complex pattern. These currents cause emissions, and depending on the resonant frequencies of the external structure (with cables etc.) will radiate more or less efficiently. The radiation does not necessarily leave the opening, seam, or air vent and radiate directly to the receive antenna. This is why emissions often seem to come from a corner of the enclosure where there is no opening, or even from a metal side panel with no seams. The radiation direction is determined by the entire external system, not the point of leakage.

I/O wires and cable allow internal signals to travel to the outside of the enclosure directly. These signals may be the intended signals, but are often unintended signals that couple onto the I/O traces or connector pins inside the enclosure. Once the unintended signals are on the external cables, they will radiate based on the resonances of the external cable lengths and shapes.

Note that while a straight wire has a resonant frequency (as described earlier), when the wire/cable is bent that resonant frequency changes because the RF current distribution changes. Typically, EMC emissions test procedures require that the external cables be bent in different shapes and their positions changed to optimize the emissions at all frequencies. This requirement is effectively changing the cables resonant frequencies to make them a more efficient radiator.

## 2.5.2 Unshielded Products

Some products do not include a metal enclosure. This is typical for low cost products where the cost of a metal enclosure is too high. In this case, the PC board can radiate directly, or signals can couple onto the attached cables/wires (as in the shielded case).

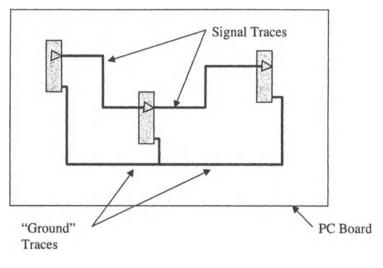

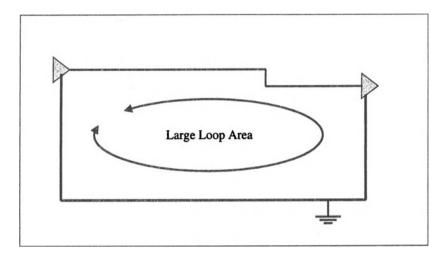

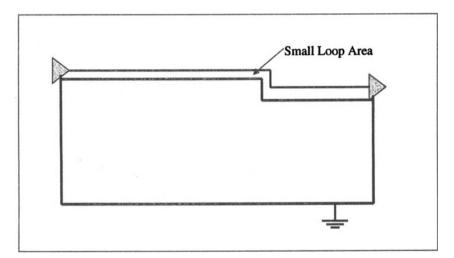

Emissions from the PC board can be significant. Energy coupled onto heatsinks and external traces will cause emissions. Often, products that are very cost sensitive will use single or double layer PC board stackup, which eliminates the benefits of solid power and ground-reference planes. The return currents from intentional signals must be routed as traces, and the loop created by the driving trace and the return trace can cause direct emissions.

# 2.6 Intentional Signal Content

One of the most fundamental facts concerning emissions is that *current* causes emissions, not *voltage*. As engineers, we tend to focus on voltage waveforms and not the current waveforms. This is sufficient if we are dealing in purely resistive circuits, but this is seldom the case. CMOS IC devices have a very different current waveform than the voltage waveform. In addition, if nonlinear devices are included, such as clamping diodes, the amount of current, especially at high frequencies, can be significant.

High frequencies tend to radiate more than low frequencies. This is mostly due to the fact that resonant effects and parasitic elements are more effective at higher frequencies. If the energy is not created to begin with, it cannot be coupled though a parasitic element, nor will it excite a resonance and ultimately cause an emission. The most cost effective way to control emissions is at their source, and to control the spectrum of the intentional signal currents. Chapter 6 will discuss this in much greater detail.

# 2.7 Summary

EMC is not magic. Effective control of EMC emissions require an understanding of the signal harmonic spectrum of the intentional currents, and how parasitic capacitance and inductance can cause these currents to flow in areas where they were never intended. When intentional currents flow on metal surfaces where they were never intended, natural resonances of those metal parts can significantly increase the emissions.

# References

[2.1] Harrington, R.F., "Time-Harmonic Electromagnetic Fields," McGraw-Hill, 1961.

# **Chapter 3**

# What is Inductance?

# 3.1 Introduction

While many of us feel that we understand it, in reality inductance is a commonly misunderstood concept. Inductance is important to EMI/EMC design considerations since it is one of the primary limiting factors in high-frequency design. Whenever there is metal, and current flows though that metal, inductance is present and will affect the current flow. At high frequencies, this intrinsic inductance dominates all components, traces, and metal planes. Capacitors and resistors become inductors.

A complete study of inductance would fill at least one entire book. The purpose of this chapter is to help the reader better understand the concepts of inductance, mutual inductance, and partial inductance as they apply to EMI/EMC design, especially on printed circuit (PC) boards.

# **3.2 Electromagnetic Induction**

When the current in a loop changes with respect to time, the magnetic field associated with that current also changes. As this changing magnetic field cuts through a conductor it induces a voltage in the circuit of that conductor. This occurs whether the magnetic field lines cut through a different conductor or the same conductor as the original current. The voltage induced in a single wire loop is equal to the time rate of change of magnetic flux passing

through the wire loop. [3.1] This is described in Faraday's law of electromagnetic induction as:

$$\oint \vec{E} \cdot dl = -\iint \frac{\partial \vec{B}}{\partial t} \cdot d\vec{S}$$

(3.1)

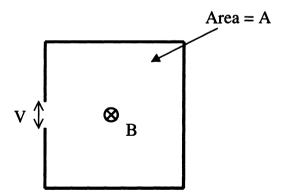

Figure 3-1 shows a simple rectangular loop. If the loop is small compared to the wavelength of the frequency of interest, then it can be assumed that the magnetic flux is constant over the area A, and Equation (3.1) can be reduced to

$$V = -A \frac{\partial B}{\partial t} \tag{3.2}$$

The amount of voltage induced from a time-varying magnetic field can be found for any geometry using Equation (3.1) and for a simple rectangular loop using (3.2).

Figure 3-1 Rectangular Loop

# 3.3 Mutual Inductance

The mutual inductance of real world circuits is often difficult to calculate since the loops are seldom simple geometries, and other metal in the surrounding environment will affect the way the fields behave. If it is assumed that two loops are located in free space (electrically far from other conductors) then the problem is simplified and a reasonable estimate can be made. Under these conditions, the mutual inductance between the two loops is defined as

$$M_{12} = \frac{\int \vec{B}_1 \cdot d\vec{S}_2}{I_1}$$

(3.3)

where:

$I_1$  = the current flowing in loop #1, B = the magnetic flux created by the current in loop #1, and S2 = the surface of loop #2.

In Equation (3.3) the magnetic flux from the current in the first loop is integrated across the surface of the second loop to find the mutual inductance.

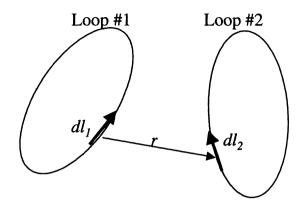

An alternative form for the mutual inductance may be obtained from vector potential formulations [3.2]. This provides the Neumann form of the mutual inductance of two loops as a double integral around the contours of both loops, in free space, as

$$M = \frac{\mu_0}{4\pi} \oint_{C_1} \oint_{C_2} \frac{d\vec{l}_1 \cdot d\vec{l}_2}{r}$$

(3.4)

where

r = the distance between contour integration elements in loop #1 and loop #2 as shown in Figure 3-2.

Figure 3-2 Two Arbitrary Loops

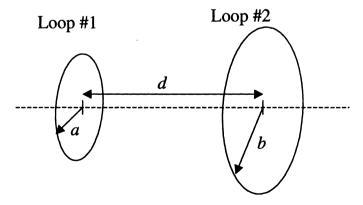

The mutual inductance of any general combination of loops can be found from Equation (3.4). For the special case of two circular loops orientated coaxially (as shown in Figure 3-3) and when a  $\ll$  d and b  $\ll$  d, Equation (3.4) can be approximated [3.3] by

$$M = \frac{\mu_0 \pi a^2 b^2}{2(b^2 + d^2)^{3/2}}$$

(3.5)

Figure 3-3 Two Loop Coaxial Oriented

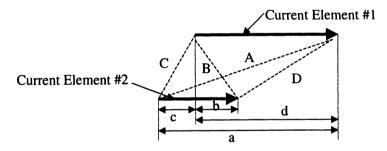

Another special case is to find the mutual inductance between two parallel current elements displaced from each other as shown in Figure 3-4. Reference [3.3] provides the Equation (3.6) for the mutual inductance. Distances A through D and overlap distances a through d are indicated in Figure 3-4. The resulting expression is useful to find the mutual inductance between square loop structures, adjacent PC board traces, etc.

$$M = \frac{\mu_0}{4\pi} \left[ \ln \frac{(A+a)^a (B+b)^b}{(C+c)^c (D+d)^d} + (C+D) - (A+B) \right]$$

(3.6)

Note that while  $\mu_0$  is used in all these equations, if the media is anything other than air, then the appropriate permittivity ( $\mu$ ) for that material must be used.

Figure 3-4 Two Parallel and Offset Conductors

# **3.4 Self-Inductance**

Recall from the previous sections that induction occurs when a timechanging current causes magnetic lines of flux to cut through metal conductors. Until now, only the case where these lines of flux caused by a current in one loop cut through the conductors of another loop was considered. These lines of flux will also cut through the conductors of the original loop as well. This gives rise to the loop's self-inductance.

The self-inductance of an isolated circular current loop in free space can also be found using Equation (3.4) if the two loops are considered to be overlapping. The difference in loop radii is considered to be equal to the radius of the wire of the single loop avoiding a singularity in Equation (3.4). For a simple isolated current loop, where the wire radius  $r_0$  is much smaller than the loop's radius *a*, then the loops self inductance is approximated as

$$L \approx \mu_0 a \left( \ln \frac{8a}{r_0} - 2 \right) \tag{3.7}$$

If multiple turns of the wire loop are used, then the inductance is simply multiplied by the number of turns to find the total inductance of the number of loops.

For an isolated square loop in free space, the self-inductance can be found from Equation (3.4) using

$$L = \frac{2\mu_0 a}{\pi} \left( \ln \frac{p + \sqrt{1 + p^2}}{1 + \sqrt{2}} + \frac{1}{p} - 1 + \sqrt{2} - \frac{1}{p} \sqrt{1 + p^2} \right)$$

(3.8)

where  $p = a/r_0$  a = length of side, and $r_0 = \text{wire radius.}$

For the case where the wire radius is much smaller than the loop radius ( $r_0 \ll a$ ), Equation (3.8) reduces to

$$L = \frac{2\mu_0 a}{\pi} \left( \ln \frac{2p}{1+\sqrt{2}} - 2 + \sqrt{2} \right)$$

(3.9)

Note that for these calculations of self-inductance the contribution by the internal flux within the conductor has been neglected. This term is most important at low frequencies when skin

depth is not important and the current is uniformly distributed across the cross section of the conductor. This self-inductance from the internal flux is given as a per-unit-length parameter as

$$L_{\rm int}' = \frac{\mu_0}{8\pi} \tag{3.10}$$

This term is then multiplied by the loop length to find the total contribution of the internal flux.

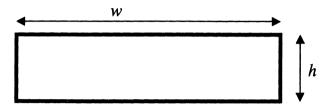

For a single turn rectangular loop in free space (Figure 3-5), the self-inductance can be found from

$$A = h \ln \left( \frac{h + \sqrt{h^2 + w^2}}{w} \right)$$

$$B = w \ln \left( \frac{w + \sqrt{h^2 + w^2}}{h} \right)$$

$$C = h \ln \left( \frac{2h}{a} \right) + w \ln \left( \frac{2w}{a} \right)$$

$$L = \frac{\mu_0}{\pi} \left( -2(w+h) + 2\sqrt{h^2 + w^2} - A - B + C \right)$$

(3.11)

where w = the width of the rectangle (wide dimension) h = the height of the rectangle (short dimension), and a = the wire radius.

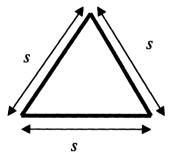

For a single equilateral triangular loop in free space (Figure 3-6), the self-inductance can be approximated from

$$L \approx \frac{3\mu_0 s}{2\pi} \left( \ln \frac{s}{a} - 1.405 \right)$$

(3.12)

where

s = the length of one side of the triangle, and a = the wire radius,

Figure 3-5 Single Turn Rectangular Loop

Figure 3-6 Single Equilateral Triangular Loop

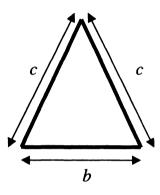

For a single isosceles triangular loop in free space (Figure 3-7), the self-inductance can be approximated from

$$A = 2(b+c)\sinh^{-1}\left(\frac{b^{2}}{\sqrt{4b^{2}c^{2}-b^{4}}}\right)$$

$$B = 2c\sinh^{-1}\left(\frac{2c^{2}-b^{2}}{\sqrt{4b^{2}c^{2}-b^{4}}}\right) - (2c+b)$$

$$L \approx \frac{\mu_{0}}{2\pi}\left(2c\ln\left(\frac{2c}{a}\right) + b\ln\left(\frac{2c}{a}\right) - A - B\right)$$

(3.13)

where

c = the length of the equal sides of the triangle,

b = the length of the base of the triangle, and

a = the wire radius.

Figure 3-7 Single Isosceles Triangular Loop

## 3.4.1 Self-Inductance per Unit Length

There are a number of special structures that are commonly of interest to EMI/EMC engineers. Many of these special structures lend themselves nicely to per-unit-length parameters, such as pair of wires, traces over ground-reference planes, etc. This section will provide estimates of the self inductance for a few special structures.

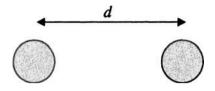

For a pair of wires in free space (Figure 3-8) with the separation much greater than the wire radius ( $a \ll d$ ), the self-inductance can be approximated from

$$L \approx \frac{\mu_0}{\pi} \cosh^{-1} \left( \frac{d}{2a} \right)$$

(3.14)

where a = the wire radius, and d = the separation from the center of the wires.

radius = a

## Figure 3-8 Pair of Wires in Free Space

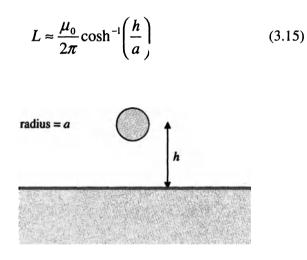

For a wire over a metal plane in free space (Figure 3-9) with the separation much greater than the wire radius  $(a \ll h)$ , the self-inductance can be approximated from

Figure 3-9 Wire Over a Metal Plane

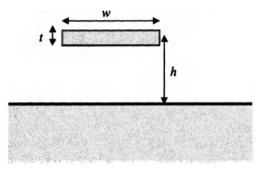

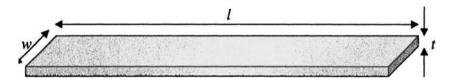

For a flat trace over a metal plane in free space (Figure 3-10), with the width of the trace much greater than the height above the metal plane  $(h \ll w)$  and the height above the metal plane greater than the thickness of the trace (h > t), the self-inductance can be approximated from

$$L \approx \frac{\mu_0 h}{w} \tag{3.16}$$

where w = the width of the trace, h = the height of the trace above the metal plane, and t = the thickness of the trace.

Figure 3-10 Trace Over a Metal Plane

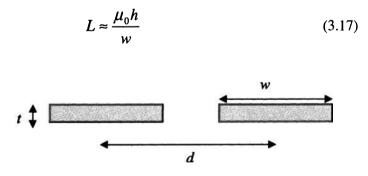

For two flat traces in free space (Figure 3-11), with the width of the trace much larger than the separation between traces  $(h \ll w)$  and the separation of the traces is greater than the thickness of the trace (h > t), the self-inductance can be approximated from

Figure 3-11 Two Flat Traces in Free Space

For two flat co-planar traces in free space (Figure 3-12), with the width of the trace much smaller than the distance between the center of the traces ( $w \ll d$ ) and the width of the traces is greater than the thickness of the trace (w > t), the self-inductance can be approximated from

$$L \approx \frac{\mu_0}{\pi} \cosh^{-1}\left(\frac{d}{w}\right)$$

(3.18)

Figure 3-12 Two Flat Co-planar Traces

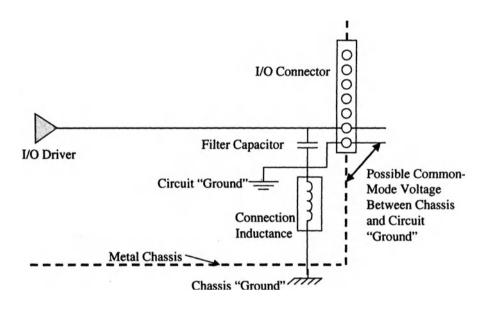

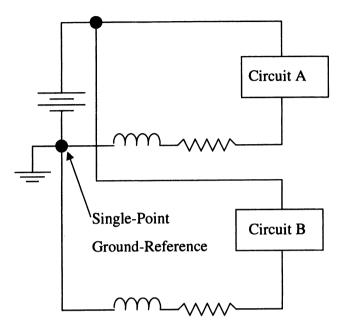

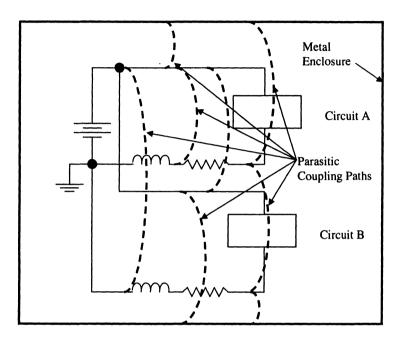

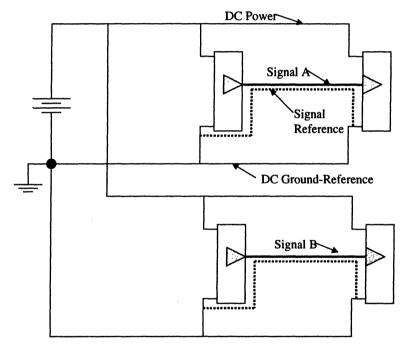

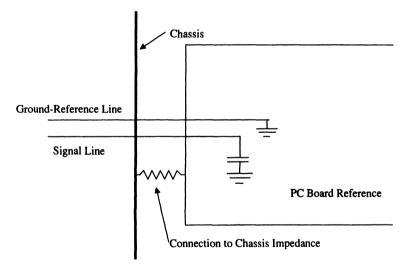

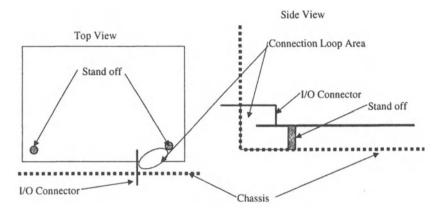

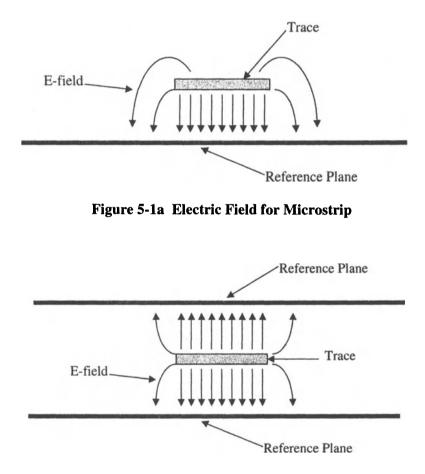

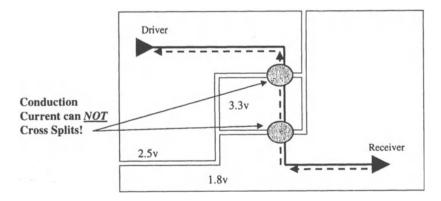

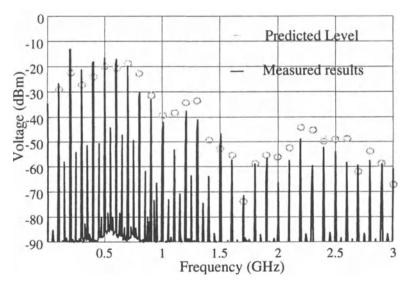

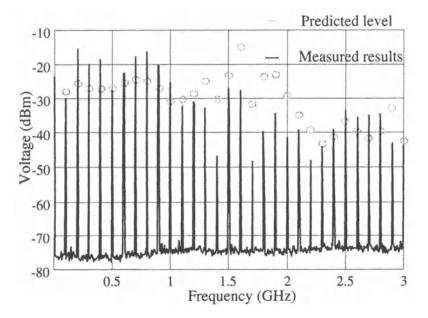

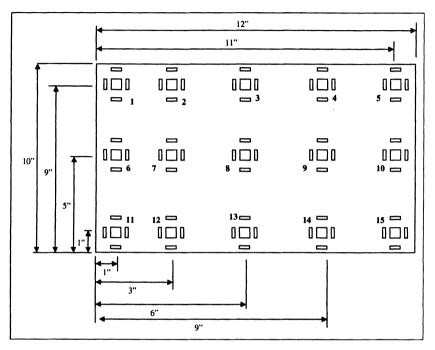

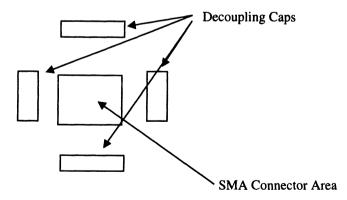

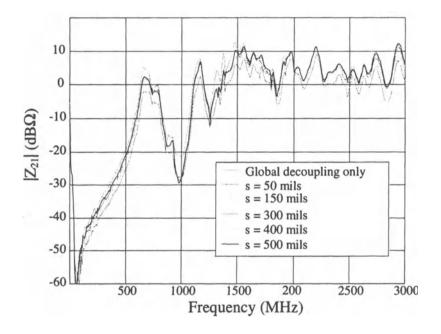

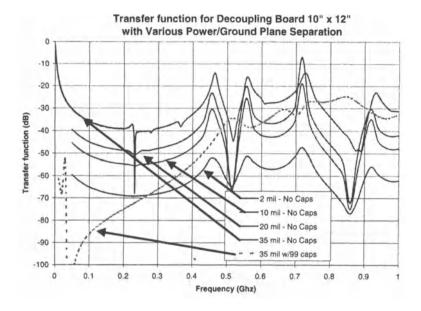

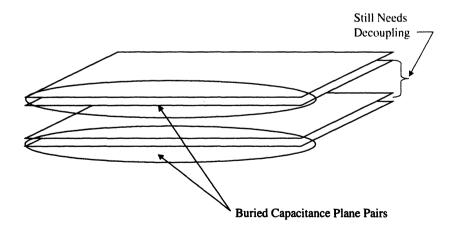

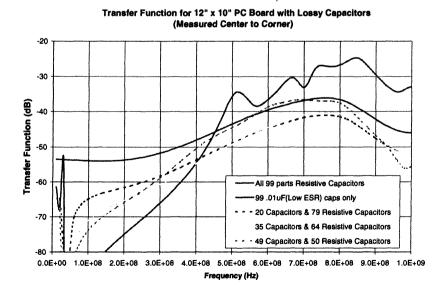

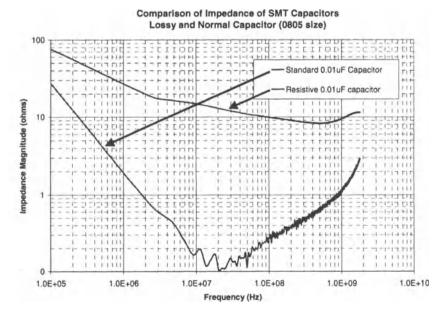

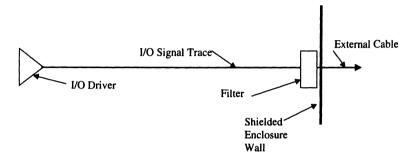

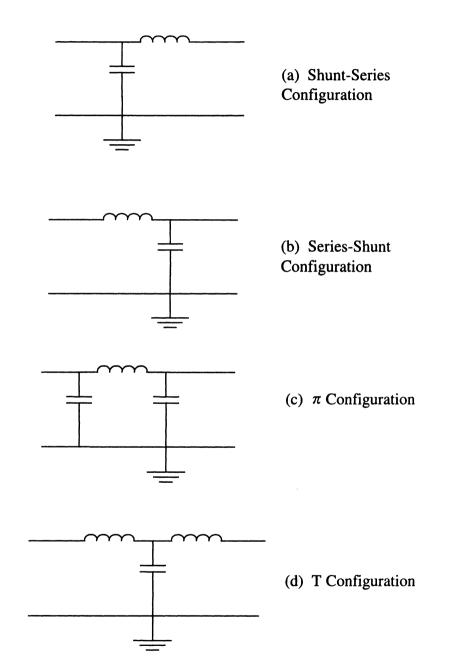

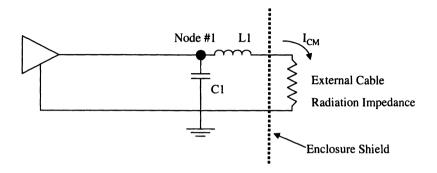

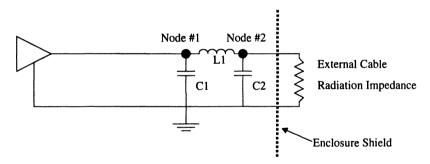

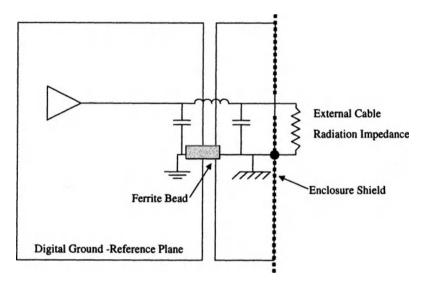

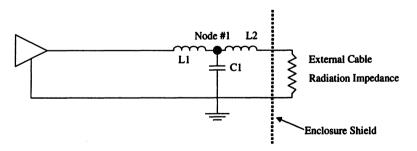

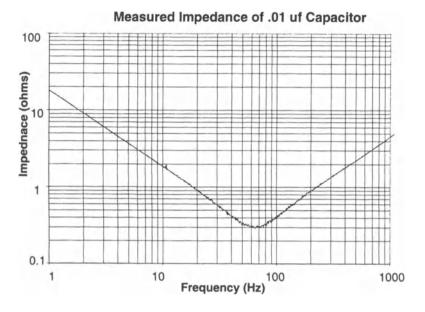

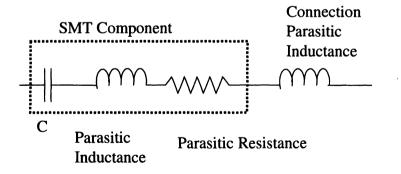

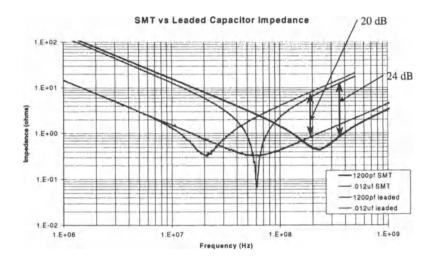

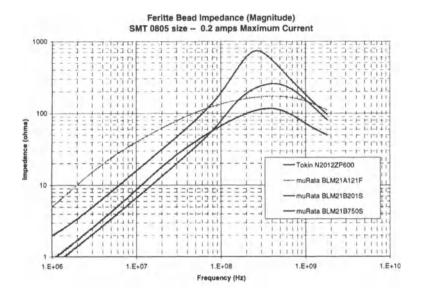

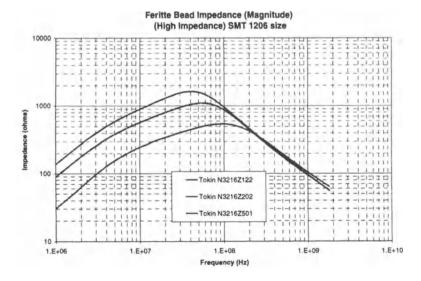

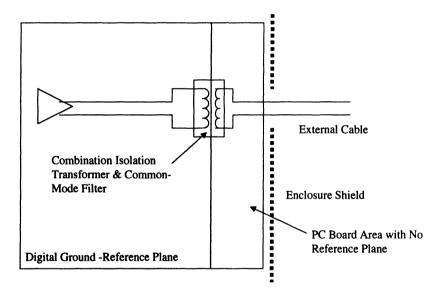

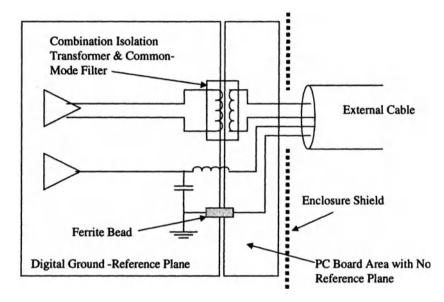

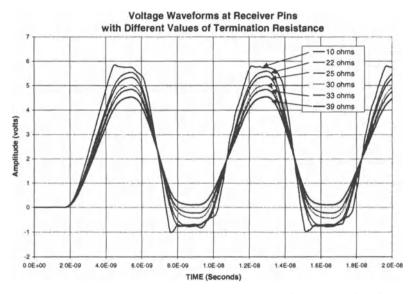

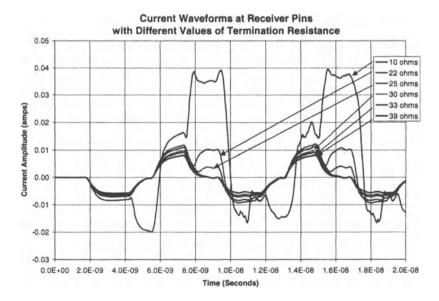

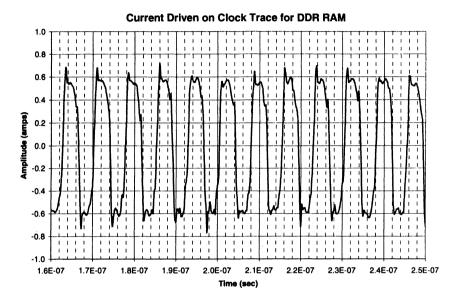

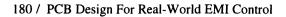

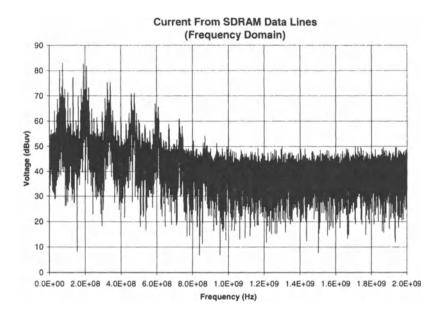

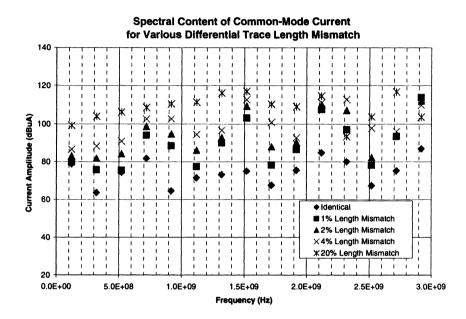

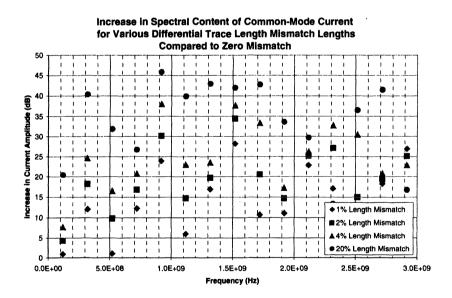

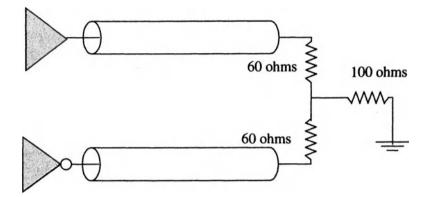

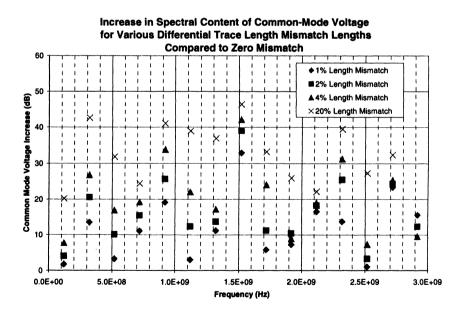

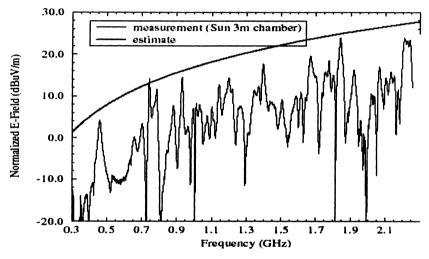

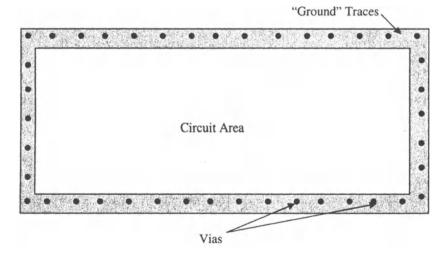

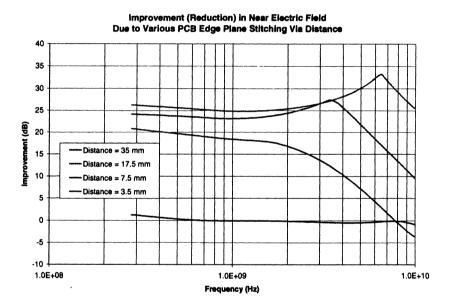

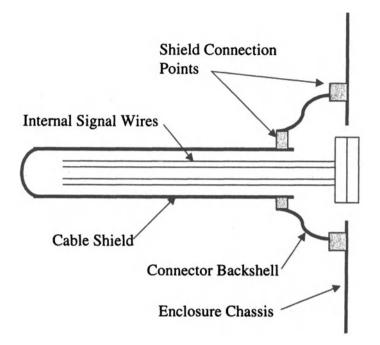

# **3.5 Partial Inductance**