# 印刷电路板(PCB)设计指南

A Brief Guide for PCB Design and Layout (Part-1)

2018年-9月7日

## Part1: 通用电路篇

- 一、引言

- 二、PCB基础知识

- 三、PCB设计步骤和规范

- 四、电流路径分析

- 五、常见类型PCB设计

## Part2: 高速电路篇

- 六、传输线与阻抗匹配

- 七、信号完整性

- 八、电源完整性

- 九、时序与信令完整性

- 十、新型PCB工艺及技术

# 一、引言

#### 注意: 本课程不是PCB软件使用教程!

#### 目前三大主流PCB设计软件

- Altiun-Designer: 轻量化的PCB设计软件,价格便宜,适合小企业、新手学习入门

- Mentor-PADS: 中高端软件,功能强大,价格适中,用户群广

- Allergo-Candence: 专业级的PCB设计软件,适合大规模复杂电路设计,价格昂贵

网上有大量的软件使用、学习、视频资源,建议自学软件知识

# ·、引言

## 会用软件, 能够"布通"是远远不够的!

- 为什么我的电路仿真OK, 实际却精度很差?

- 为什么ADC数据的跳动(噪声)那么强烈?

- 为什么我的放大器电路会自激或啸叫?

- 为什么数字电路总是出现莫名其妙逻辑错误?

- 为什么我的单片机控制板总是死机、跑飞?

- 驱动1A的负载, 我应该要用多粗的导线?

- 220V电源入口, 绝缘间距取多少合适?

- 为什么功率管的焊点总是烧融?

这些问题或现象都,往往都和PCB设计有关,本课程将重点 讨论PCB设计的原理性、原则性、共性的问题及解决方法!

# 目 录

## Part1: 通用电路篇

一、引言

二、PCB基础知识

三、PCB设计步骤和规范

四、电流路径分析

五、常见类型电路设计

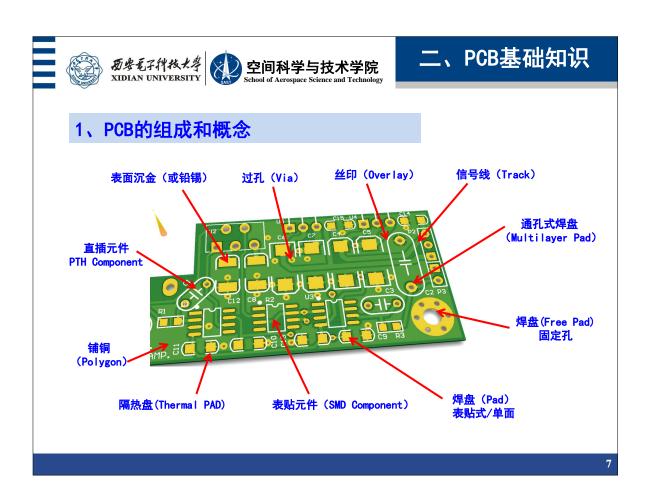

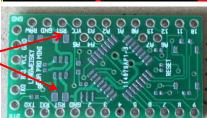

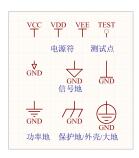

#### 3、PCB易混淆的概念

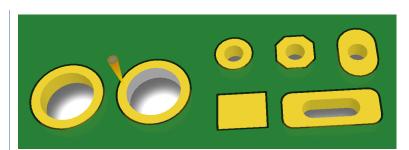

#### A. 过孔(Via)和焊盘(Pad)

#### 过孔(Via)

- 作为导线换层的 连通器使用

- 只能是圆形

- 必须是镀孔

- 必须在Multi层

#### 焊盘(Pad)

- 形状灵活的多:圆、椭圆、方形、长条、八边形

- 可选镀孔(连接孔)/非镀孔(作为固定孔)

- 可开异型孔,便于插入特殊扁平针脚元件

- 可以在Multi层(直插件),也可单层(SMD元件)

9

面安笔子科技大学 XIDIAN UNIVERSITY

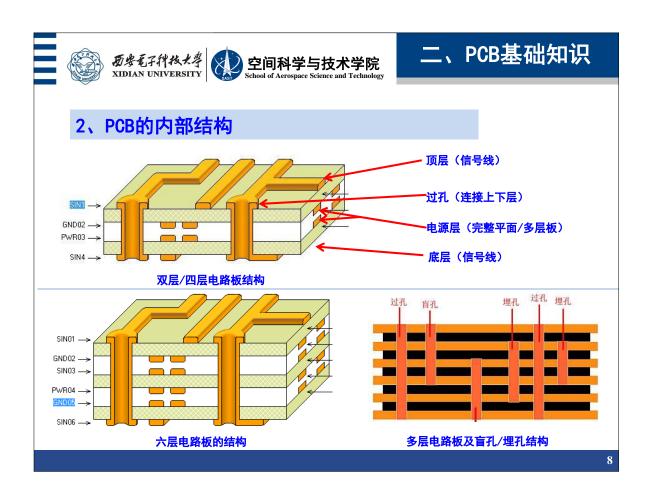

# 二、PCB基础知识

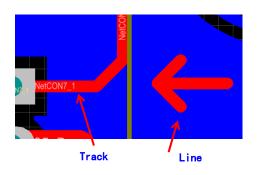

#### 3、PCB易混淆的概念

#### 线(Line)

- 只是一个线

- 不具备电路节点对应关系,但在信 号层的话,仍会导电

- 布线时不会被推挤、移除

- 任何层都可画线

#### B. 线(Line)和导线(Track)

手动布线时,使用自动推挤功能使Track自动避让

#### 导线(Track)

- 导线具有和原理图对应的网络连接关系

- 导线带有网标(NetLable),对应电路图节点

- 在布线时,导线可以被自动推挤、环绕等

- 只有在信号层才能画导线

## 1、PCB层(Layer)的分类

#### A. 导电层

- 顶信号层(Top Layer)

- 底信号层 ( Bottom Layer )

- 内层(Internal Plane)

- 中间层 (Middle Layer)

#### C.绘图辅助层

- 禁布层(keep-out Layer)

- 多层 (Multi-Layer)

- 机械层 (Mechanical Layer)

- 钻孔层 (Drill Layer)

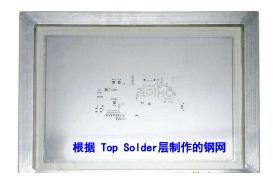

#### B. 掩模(Mask)层

- 底丝印层(Bottom Overlay)

- 顶阻焊层(Top Solder)

- 底阻焊层(Bottom Solder)

- 顶锡浆层(Top Paste)

- 底锡浆层(Bottom Paste)

13

历安笔子科技大学 XIDIAN UNIVERSITY

# 二、PCB基础知识

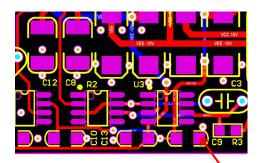

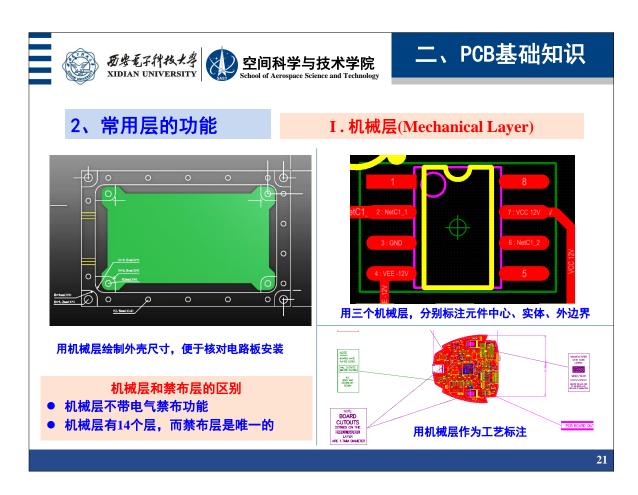

## 2、常用层的功能

# 顶层 (Top Layer) 底层 (Bottom Layer)

#### A. 信号层

顶层/元件面(Top Layer)

底层/焊接面(Bottom Layer)

#### 2、常用层的功能

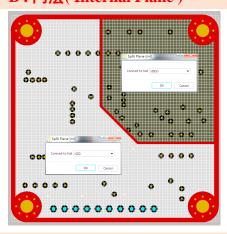

#### B.内层(Internal Plane)

#### Plane 和 Layer 的区别

- Layer: 画线部分是保留的导电铜箔,空白区域为刻蚀/绝缘区域 (阳版)

- Plane: 画线部分为刻蚀区域,空白部分为导电铜箔 (阴版)

- 注意两者刚好相反。Layer适合画信号线,Plane适合画电源层 (多层板内层)

15

历安笔子科技大学 XIDIAN UNIVERSITY

# 二、PCB基础知识

## 2、常用层的功能

## C. 丝印层(Top/Bot Overlay)

#### 丝印层的工艺和用途

- 采用丝网印刷工艺涂印

- 作为装配图、注释标记、Logo

- 作为切割、装配标记

- 局部覆盖,增加绝缘性

#### 2、常用层的功能

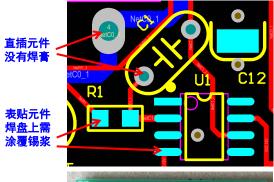

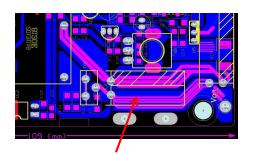

#### D. 阻焊层(Top/Bot Solder)

紫色: TopSolder 裸露部分

Solder层比焊盘 略大一些

#### 阻焊层的工艺和用途

- Solder层划线部分为裸露金属,空白部分为阻焊层(俗称绿油)

- ▶ 大电流导线可以用Solder层裸露 出来搪焊锡加厚

17

历安笔子科技大学 XIDIAN UNIVERSITY

# 二、PCB基础知识

# 2、常用层的功能

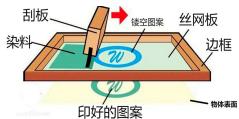

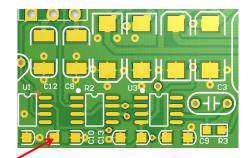

## E. 锡浆层(Top/Bot Paste)

刮完锡浆 的电路板 准备贴 元器件

#### 锡浆层的工艺和用途

- Paste层划线部分为钢网刻孔部分

- 用于SMT工艺刷锡浆

- 大电流导线可以用Solder层裸露并加 Paste锡浆加厚

# 2、常用层的功能

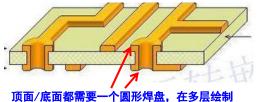

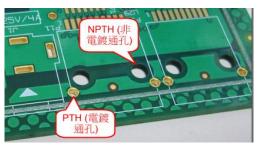

#### F. 多层(Multi-Layer)

#### 多层的用途

- 多层上画的实体在每个Layer都有(Plane除外)

- 常用于直插焊盘、过孔等需要穿透每个层

- 用于焊盘时,可定义电镀孔(PTH)和非电镀孔 (NPTH)

19

历安笔子科技大学 XIDIAN UNIVERSITY

# PCB基础知识

## 2、常用层的功能

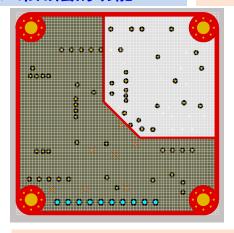

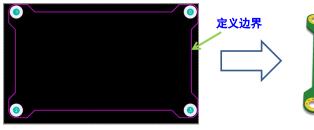

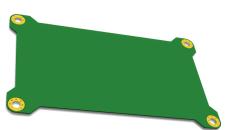

#### G. 禁布层(Keep-out Layer)

#### 定义开槽位置

#### 禁布层的用途

- 定义电路板的边界、切割线

- 定义电路板的挖空、开槽位置

- 定义不允许放置导线的区域,会自动避开

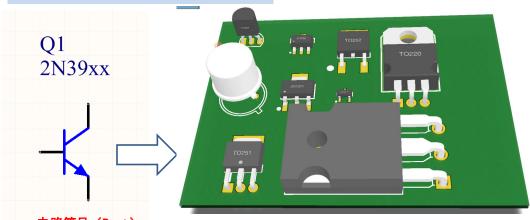

# 1、元件符号和封装

电路符号 (Part)

- PCB封装(FootPrint/Package)

- 同一个电路符号(Part),往往对应多个封装(FootPrint)

- 同一个封装,因为安装形式不同(如: 立/卧),衍生出若干子封装

- 设计时仔细核对: (1) 封装尺寸/形式是否正确; (2) 管脚顺序是否相符

23

历安笔子科技大学 XIDIAN UNIVERSITY

# 二、PCB基础知识

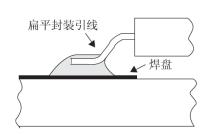

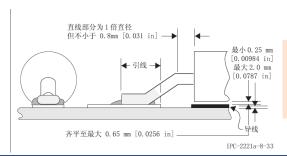

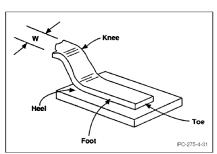

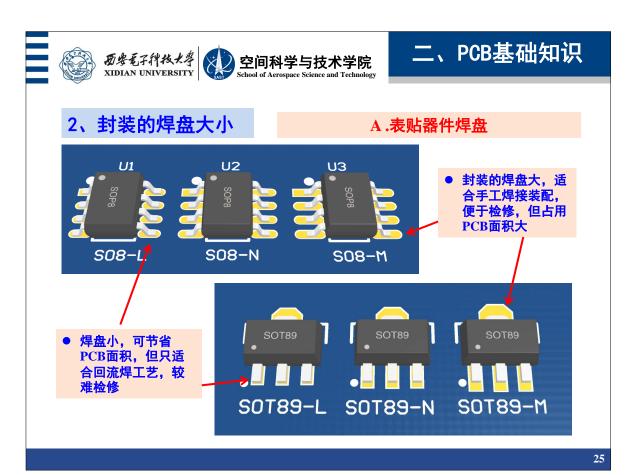

#### 2、封装的焊盘大小

#### A.表贴器件焊盘

Figure 8-35 Heel mounting requirements

- ▶ 焊盘应大于引脚接触面积,留出装配误差

- ▶ 沿长度方向,延长0.5-1.5倍,便于拉锡处理

- 宽度方向,注意焊盘间距,保证绝缘和涂覆 焊膏最小间隙

## 2、封装的焊盘大小

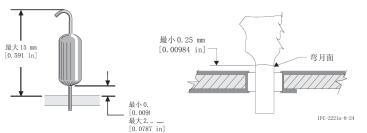

#### B.直插器件焊盘

安装焊盘及应力释放孔

- 孔环不得低于最小加工能力,还要考虑钻孔误差

- 较重、或受力、承重的器件、焊盘直径要加粗、避免扯裂焊盘

- 焊盘加粗时, 若焊盘间的间距不足, 可考虑椭圆形加粗

- 小元件腿与通孔隙件至少0.1mm, 频繁拆卸的器件, 通孔要加大, 与元件腿之间最小缝隙0.2mm以上

- 紧固件焊盘,建议增加一圈过孔,缓解PCB形变的应力

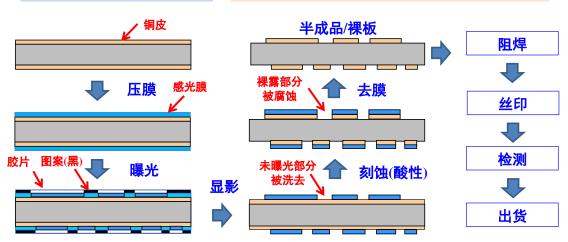

#### 1、PCB工艺概览

#### A.酸性蚀刻法(负片)

- (1)开料----(2)钻孔----(3)镀孔----(4)涂感光油墨----(5)图形转移(曝光)----

- (6)显影-----(7)蚀刻----(8)去膜——(9)检查

#### B.碱性蚀刻法(正片)

- (1)开料----(2)钻孔----(3)镀孔----(4)涂感光油墨----(5)图形转移(曝光)----

- (6)显影-----(7)电镀锡[抗蚀层]----(8)去膜----(9)蚀刻----(10)去锡----(11)检查

#### C.后处理

- (1)印阻焊/绿油----(2)印字符----(3)金属表面处理----(4)成品成型----(5)电测试-----

- (6)外观检查---(7)包装出货。

29

历安笔子科技大学 XIDIAN UNIVERSITY

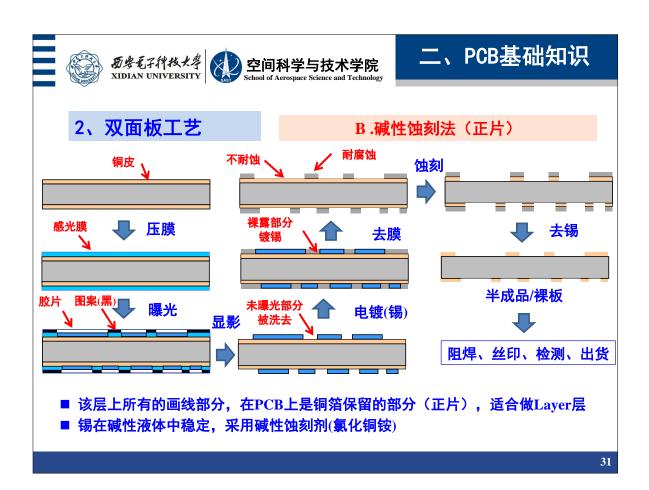

# 二、PCB基础知识

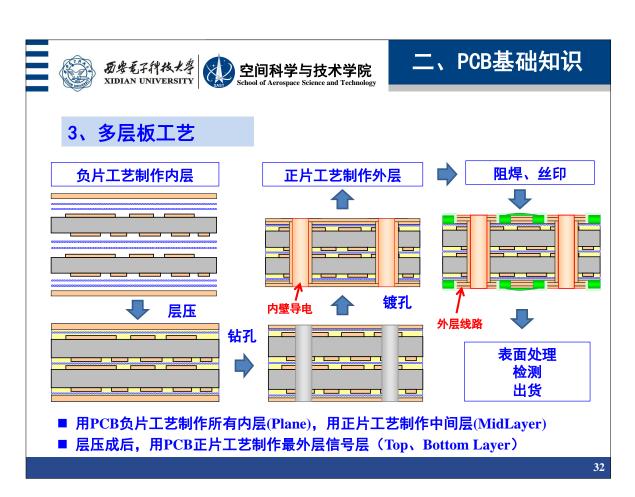

## 2、双面板工艺

#### A.酸性蚀刻法(负片)

- 该层上所有的画线部分,在PCB上是铜箔被挖去的部分(负片),也适合Plane层

- 镀膜酸性稳定,采用酸性蚀刻剂(酸性CuCl<sub>2</sub>、盐酸+双氧水/氯酸钠,FeCl<sub>3</sub>已淘汰)

#### 4、工艺极限

- 曝光能力和腐蚀的扩散效应,限制了最小线宽

- 电镀孔工艺,限制了过孔/焊盘的最小内径(PCB越厚,孔径越大)

- 层间对准误差、钻孔位置误差,限制了焊盘、过孔的最小外径

- 腐蚀工艺的洁净度,限制了导线间的最小间距

- 特殊新工艺,如激光钻孔、沉积板,能够达到2mil极限,但是价格昂贵

#### 大部分厂家1.6mm双面板的加工极限

| 类型   | 可靠值             | 一般值             | 极限值             |

|------|-----------------|-----------------|-----------------|

| 最小线宽 | 8-10mil         | <b>4-6mil</b>   | 2-4mil          |

| 最小间距 | 10mil           | 6-8mil          | 4mil            |

| 最小过孔 | (16-20)/(36-40) | (12-16)/(24-32) | (10-12)/(20-24) |

- 极限值:通过苛刻的条件能达到,但不宜大批量生产。

- 一般值:可以大批量生产,但需要特殊工艺保证良品率,要收取额外的工 艺费和测试费,会增加成本和交货周期;

- 可靠值:可以大批量可靠生产。【仅供参考,以厂家沟通为准!】

33

#### Part1: 通用电路篇

PCB基础知识

三、PCB设计步骤和规范

四、电流路径分析

五、常见类型电路设计

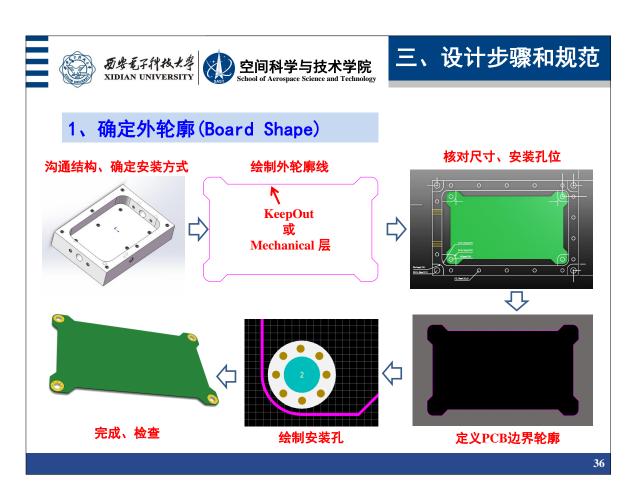

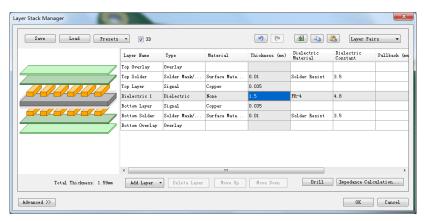

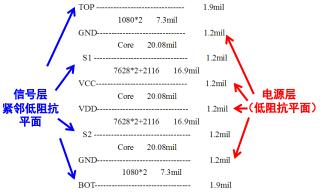

#### 2、设置LayerStack

- 设置基板和每层材料的介电特性、厚度:

- (1) 这是后续特征阻抗分析、信号完整性的重要参数依据

- (2) 给制版厂家的重要数据

- PCB行业用Oz(盎司)表示铜箔厚度, 1Oz=35um【类似于打印纸厚度用70g表示】

37

历安笔子科技大学 XIDIAN UNIVERSITY

# 三、设计步骤和规范

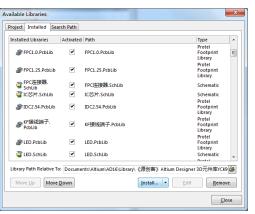

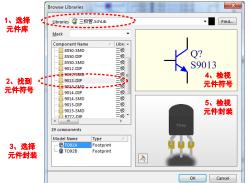

#### 3、准备元件库

检查所需元件的

电路符号和封装

是否对应、齐全

载入库文件:

- (1)软件自带有基本库文件

- (2)第三方购买专业的库 (3)元件共享网站下载 ->连接

- (4)特殊元件自行绘制【参考软件教程】

有多重封装的器件, 要仔细核对所选封装及 管脚顺序!

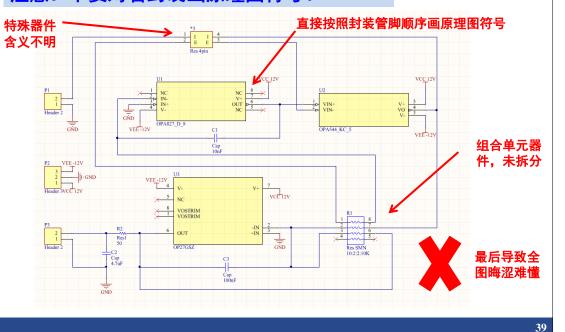

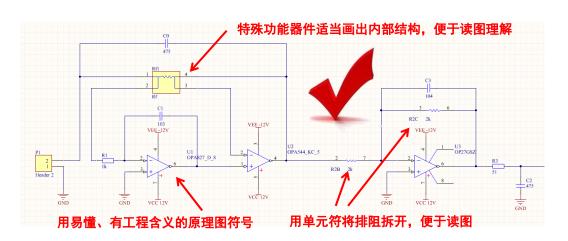

## 注意: 不要对着封装画原理图符号!

# 三、设计步骤和规范

#### 注意:不要对着封装画原理图符号!

——原理图应该便于"读图",而非追求和实际器件排布**一**致

#### ! 注意检查!

- (1) 元件符号的正确性、元件符号和所选用封装的对应性

- (2) 元件封装的管脚顺序,是否和实际元件的功能排列一致? (3) 元件应该具有唯一标号【若使用自动标注,可用?替代】

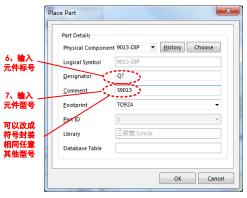

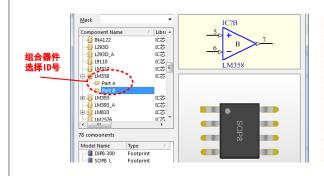

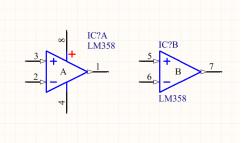

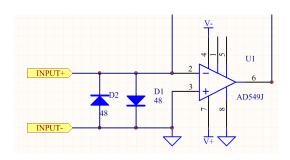

#### 1、放置元件

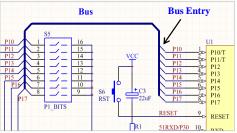

#### B.放置多单元组合型器件

组合器件(如双运放、六反相器、多路光耦)含有多个的相同功能单元,应该按 单元ID来逐部分放置器件,以便绘图灵活调整连接关系和布局

43

# 三、设计步骤和规范

#### 1、放置元件

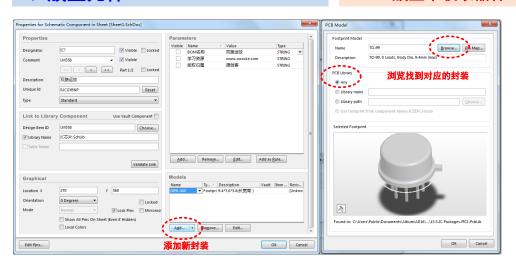

#### C.放置未收录器件

特殊封装的器件,自行绘制或下载后添加入库,建立对应关系;检查管脚对应

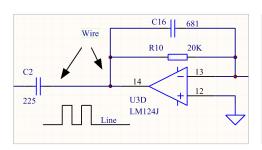

#### 2、电气连线(Wire)

#### A.原理图绘制的四种线类型

- (1) Wire: 具有电气连接功能的"导线",用于绘制原理图

(2) Line: 不具备电气连接功能的"图线",用于绘制各种标识

(3) Bus: 不具备电气连接功能的"总线",用于指示总线线束的走向

(4) Bus Entry: 具备电气连接功能的45度短线,表示"线束入口"

45

历安笔子科技大学 XIDIAN UNIVERSITY

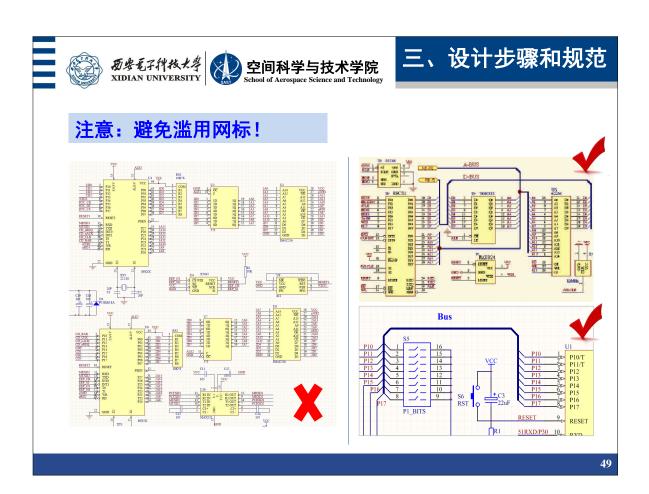

# 三、设计步骤和规范

## 2、电气连线(Wire)

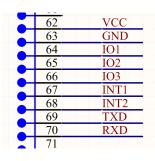

#### B.网标(NetLabel)

- 放置了相同网标的导线,电气连接在一起【不必实际画线】

- 放置网标后,该电路节点被命名为网标名【后续制定布线规则可以引用】

- 电源、地线应该用尽量用网标表示,以保持图面简洁【有专用网标符】

- 网标要整个放置在导线上【绘图规范】

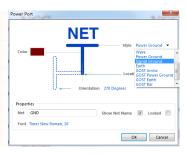

# 2、电气连线(Wire)

#### C.端口(Port)

- Port 也具有和网标相同的功能, Port名相同的导线表示连接在一起

- Port 还能够指示输入、输出关系, (I/O Type)

- Port符号一般用在:

- (1) 分图之间的连接关系

- (2) 表示模块单元之间的接口连接 (3) 某些特定输入/输出端口

历安冠子科技大学 XIDIAN UNIVERSITY

# 三、设计步骤和规范

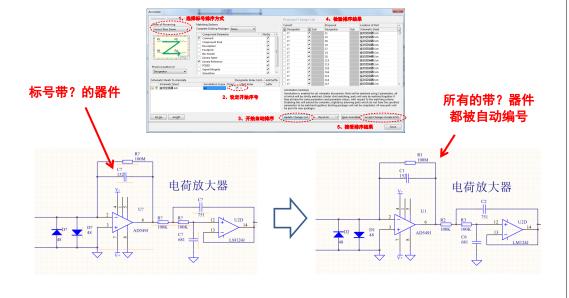

#### 3、自动标注(Auto Anotate)

# "七分布局,三分布线"

51

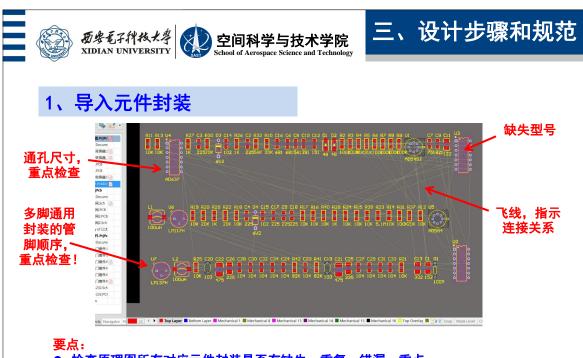

- 检查原理图所有对应元件封装是否有缺失、重复、错漏,重点

- 检查标号、型号参数等字符是否齐全

- 大图建议分批导入,原理图绘制完一部分,导入一部分、并立即检查该部分

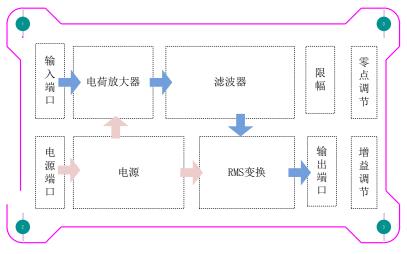

#### 2、布局总体规划

- 信号总体走向单向流动,尽量减少折返、交叉等情况

- 各种输入/输出端口、配置调节等部件尽量靠近电路板边缘,便于接线和调试操作;如果有大功率器件,从布局上要考虑通风散热,且远离温度敏感的电路部分。

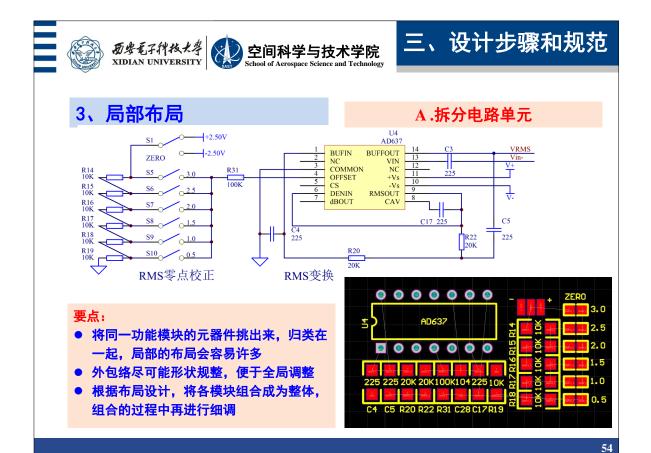

#### 3、局部布局

#### B.布局和预布线测试

完成局部布局的单元电路

尝试预布线(看布通率)

- 先确定大型器件、多管脚的器件位置,其余2-3腿小元件围绕大器件灵活调整。

- "一头近"原则:即每个小元件的飞线有一头尽量短,飞线的交叉会减少很多。

相邻小元件之间的距离间隙,以能够走1-2根线为宜。

预留一些空间放置元件的标号。元件标号字符一定要放在器件轮廓外

布局时可以先暂时隐藏掉GND、VCC等公共网络的飞线,以免扰乱视线。

55

# 三、设计步骤和规范

#### 4、整体布局

#### A. 布局的一般要求

#### 好的布局:

- (1) 元件整齐划一,便于贴装工艺生产; (2) 整体上飞线短、交叉少,后续布线工作会变得容易; (3) 功能模块划分明确,信号流向清晰。

#### 4、整体布局

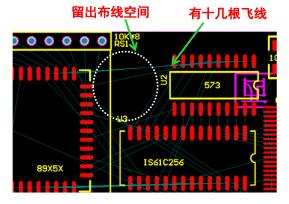

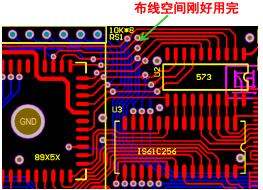

#### B. 布线空间的概念

#### 要点:

- 按照飞线数量适当地预留布线空间。

- 布线空间的大小和飞线的密集程度有关,需要一定的经验积累

- 某些管脚顺序可以灵活调节,例如IO口,避免飞线交叉过孔能节省布线空间

57

历安笔子科技大学 XIDIAN UNIVERSITY

# 三、设计步骤和规范

## 5、整体布局

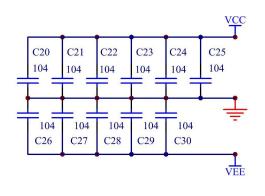

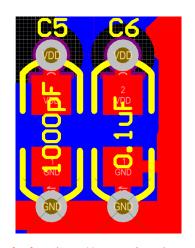

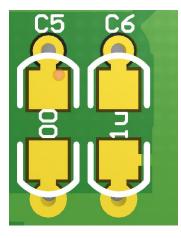

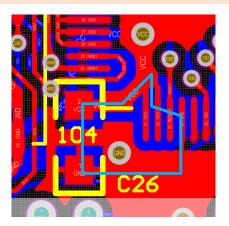

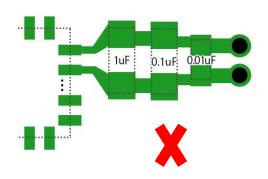

#### C. 退耦元件的处理

- 因为所有退耦器件的网标相同,原理图中放在器件附近反而会引起混乱;● 在原理图中,退耦电容集中画在一起,布局时随意取用,就近放在各IC附近● 退耦问题,在电源完整性中将详细讲解

# 不要直接使用自动布线!

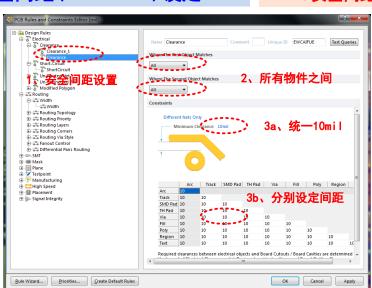

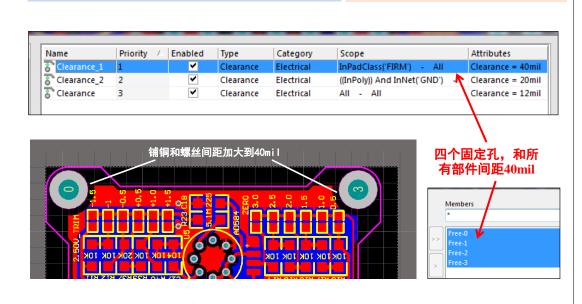

#### 1、安全间距(Clearance)设定

#### 工作条件 直流电压 裸露外层线路 裸露外层线路 阻焊包覆 交流峰值 内层线路 (海拔<3000m) (海拔>3000m) 外层线路 0-15 0.05 mm 0.1 mm 0.1 mm 0.05 mm 16-30 0.05 mm 0.05 mm 0.1 mm 0.1 mm 31-50 0.1 mm 0.6 mm 0.6 mm 0.13 mm 51-100 0.1 mm 0.6 mm 1.5 mm 0.13 mm 101-150 0.2 mm 0.6 mm 3.2 mm 0.4 mm 151-170 0.2 mm 1.25 mm 3.2 mm 0.4 mm 171-250 0.2 mm 1.25 mm 6.4 mm 0.4 mm 251-300 0.2 mm 1.25 mm 12.5 mm 0.4 mm 301-500 0.25 mm 2.5 mm 12.5 mm 0.8 mm 0.0025 mm 0.005 mm 0.00305 mm 0.025 mm > 500 /volt /volt /volt /volt

#### 要点:

- 电压越高的导线,和全板所需的安全间距越大

- 裸露部分(焊盘、过孔、元件腿)所需安全间距大

- 海拔越高,所需的绝缘间距越大

- 低压电路,参考制版厂家极限,并留余量

#### A. 安全间距规范

| 海拔    | 间距扩增因子 |

|-------|--------|

| 2000  | 1.00   |

| 3000  | 1.14   |

| 4000  | 1.29   |

| 5000  | 1.48   |

| 6000  | 1.70   |

| 7000  | 1.95   |

| 8000  | 2.25   |

| 9000  | 2.62   |

| 10000 | 3.02   |

| 15000 | 6.67   |

| 20000 | 14.50  |

61

# 三、设计步骤和规范

#### 1、安全间距(Clearance)设定

#### B. 安全间距规则设定

利用规则编辑器,进行全局安全间距设定(参考软件使用手册,及PCB厂家指导数据)

#### 2、线宽(Width)设定

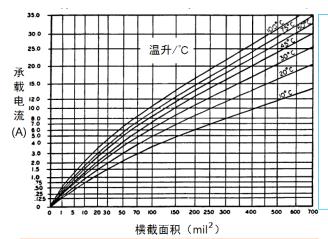

#### A. 线宽规范

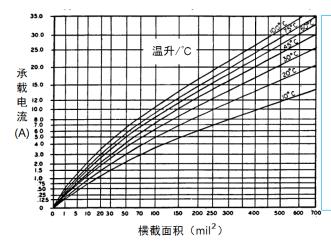

【例】导线通过10A电流,在室温25℃工作 时要控制导线表面温度不超过70℃

#### 【解】

- (1) 允许温升70-25=45℃。

- (2) **查曲线横截面积** s=150mil<sup>2</sup>

- (3) 厚度1Oz (35um,1.38mil) 的PCB,则最小线宽是150/1.38=108mil;

- (4) 采用2Oz的电路板,需要54mil线宽。

#### 要点:

- 电流越大的导线,所需的越宽

- 采用厚板、改善对流条件,可减小线宽需求

#### 注意:

- 这仅仅是从温升角度考虑线宽

- 导线阻性压降,需要结合原理考虑

63

历安笔子科技大学 XIDIAN UNIVERSITY

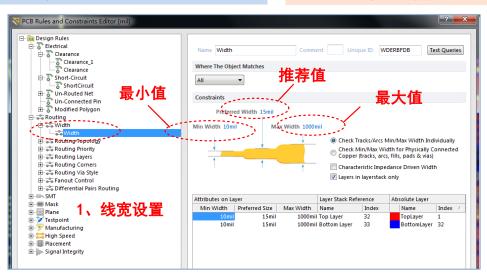

# 三、设计步骤和规范

# 2、线宽(Width)设定

#### B. 线宽规则设定

- 利用规则编辑器,进行全局线宽设定(参考软件使用手册,及PCB厂家指导数据)

- 利用类编辑器和规则编辑器,对特殊网络制定线宽规则

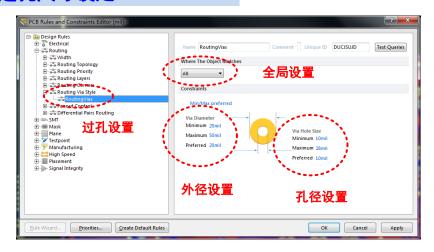

#### 3、过孔尺寸设定

- 利用规则编辑器,进行全局过孔设定(参考软件使用手册,及PCB厂家指导数据)

- 利用类编辑器和规则编辑器,对大电流过孔规则设定

- 大电流过孔计算: 查表所需横截面s, 孔周长l=s/0.7-1.0mil(18-25um);孔径d=l/π

65

# 三、设计步骤和规范

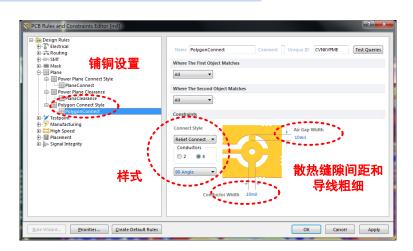

#### 铺铜连接样式设定

- 一般元器件焊盘,都要隔热缝,以免铜皮散热引起的焊接不良

- 大电流焊盘,不能加隔热缝;考虑人工焊接,或工艺上增加加热时间

- 地线过孔一般考虑直接连接,不用隔热缝

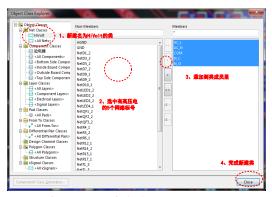

#### 规则进阶 ·类(Class)编辑器

#### A.网络类(Net Class)的使用

将其归类,命名为"HiVolt"类

| Name        | Priority | △ Enabled | Type      | Category   | Scope                      | Attributes        |

|-------------|----------|-----------|-----------|------------|----------------------------|-------------------|

| Clearance_1 | 1        | ~         | Clearance | Electrical | InNetClass('HiVolt') - All | Clearance = 60mil |

| Clearance   | 2        | ~         | Clearance | Electrical | All - All                  | Clearance = 10mil |

利用规则编辑器,将"HiVolt"网络类的安全间距增大,并把优先级调高

#### 5、规则进阶——类(Class)编辑器

#### B.焊盘类(PadClass)

封装LQFP因Pad间距太小报错

新建一PadClass包含这64个焊盘

| Name        | △ Priority | Enabled | Туре      | Category   | Scope                        | Attributes        |

|-------------|------------|---------|-----------|------------|------------------------------|-------------------|

| Clearance_1 | 1          | ~       | Clearance | Electrical | InPadclass('Pad_LQFP') - All | Clearance = 7mil  |

| Clearance_2 | 2          | ~       | Clearance | Electrical | InPolygon - All              | Clearance = 15mil |

| Clearance_3 | 3          | ~       | Clearance | Electrical | All - All                    | Clearance = 10mil |

利用规则编辑器,仅将该PadClass焊盘类的安全间距缩小,并把优先级调高

69

历安笔子科技大学 XIDIAN UNIVERSITY

# 三、设计步骤和规范

#### 5、规则进阶——类(Class)编辑器

#### B.焊盘类(PadClass)

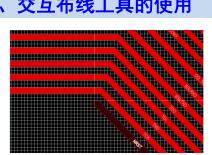

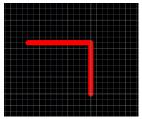

#### 6、交互布线工具的使用

模式1: Stop at First Obstacle

模式3: Walk around Obstacle

模式2: Ignore Obstacles

模式4: Push Obstacle

# 三、设计步骤和规范

#### 交互布线工具的使用

模式5: Auto Route

Line90/45 With Arc

Line90/90 With Arc

**Any Angel**

Track 45

Track 90

## 7、常用布线策略

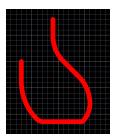

### A. 入门——Z字走线法

- 顶层、底层走线相互垂直,最大化布线空间 所有任意两点之间走 "Z" 字路径完成连接

优点: 策略最简单, 新手入门常用方法

缺点:引入大量过孔

适用: 大量直插、通孔器件的PCB设计

73

# 三、设计步骤和规范

### 7、常用布线策略

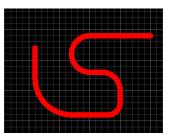

### B. 讲阶——单面走线法

- 尽可能在元件面完成走线(如顶面)

- 尽可能保持底面完整性,并作为地平面

<mark>优点</mark>:过孔少,地平面相对完整 缺点:复杂,对布局水平要求很高 适用: 表贴器件为主的双面PCB设计

### 7、常用布线策略

#### B. 进阶——单面走线法

顶面: 走完了90%以上的连接线

底面:尽量保留完整地平面

注意: 地平面的完整性和连通性,是决定性能的关键(详见第四章讲解)

历安笔子科技大学 XIDIAN UNIVERSITY

# 三、设计步骤和规范

### 7、常用布线策略

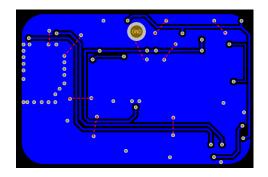

### C. 单面板

- ▼ 尽可能采用直插元件,留出布线空间● 充分利用接插件的固定脚,作为地线跳线● 实在布不通的局部,用0欧姆电阻或跳线

优点: 省钱!

缺点: 布局布线水平要求很高 适用:成本要求苛刻的PCB

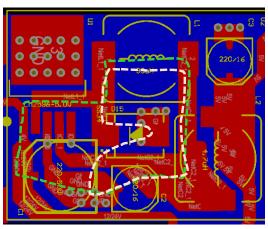

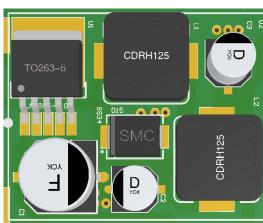

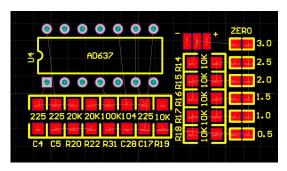

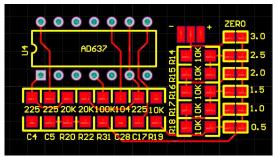

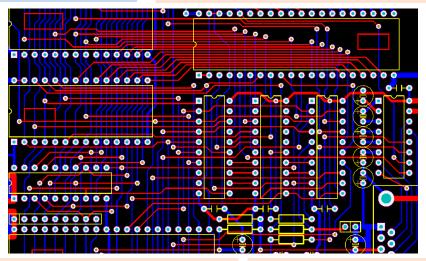

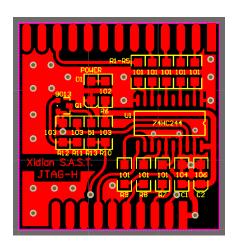

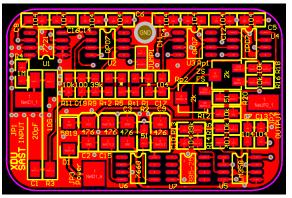

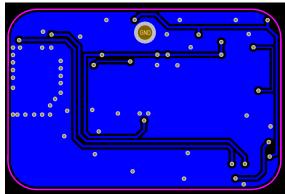

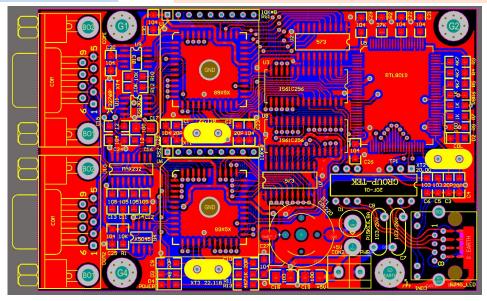

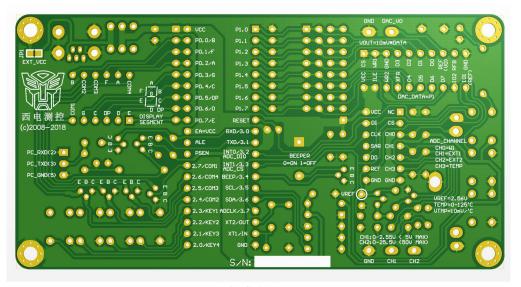

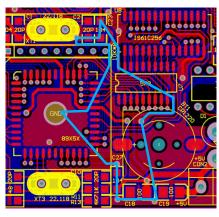

### 【PCB范例】

#### A. 纯模拟电路

·款振动/变送器

# 三、设计步骤和规范

### 【PCB范例】

### A. 纯模拟电路

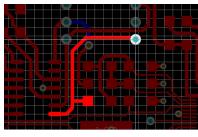

### 【PCB范例】

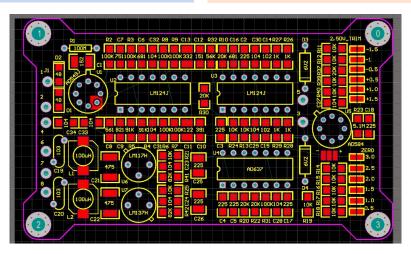

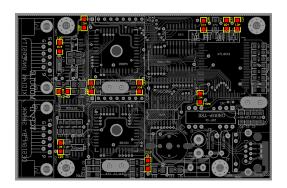

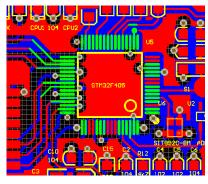

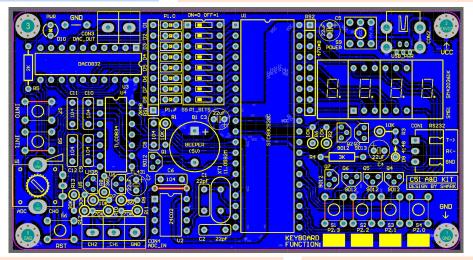

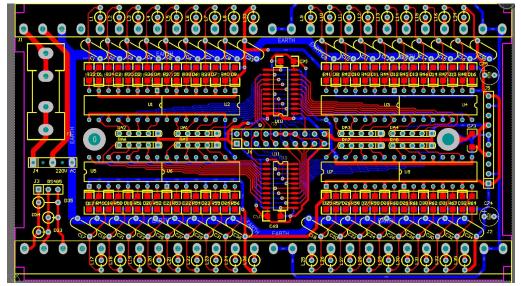

#### B. 纯数字电路

一款嵌入式通信板卡

**79**

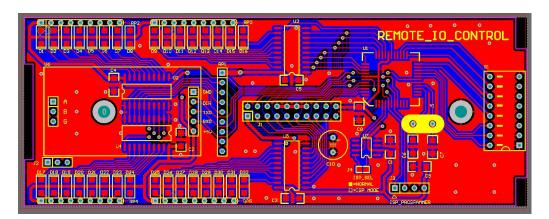

# 三、设计步骤和规范

### 【PCB范例】

### B. 纯数字电路

一款远程IO主控板卡

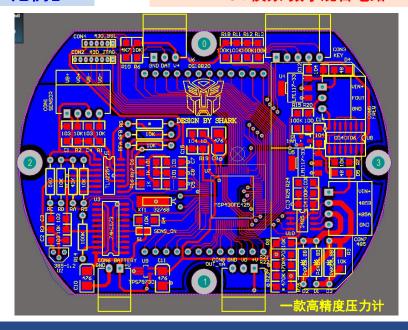

### 【PCB范例】

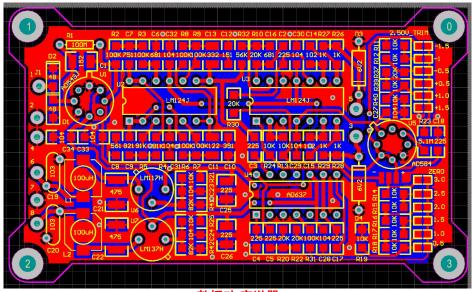

#### C. 模拟-数字混合电路

81

# 三、设计步骤和规范

### 【PCB范例】

### C. 模拟-数字混合电路

### 【PCB范例】

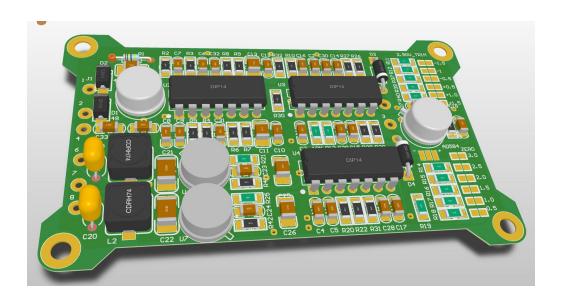

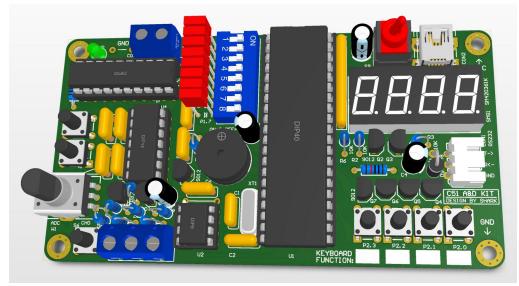

#### D. 单面板

一款低成本的开发板

83

# 三、设计步骤和规范

### 【PCB范例】

### D. 单面板

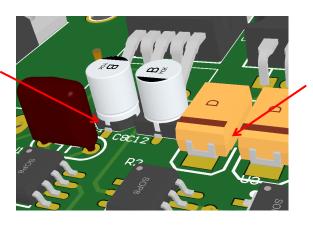

采用Solidworks建模 + Altium 3D渲染模式

### 【PCB范例】

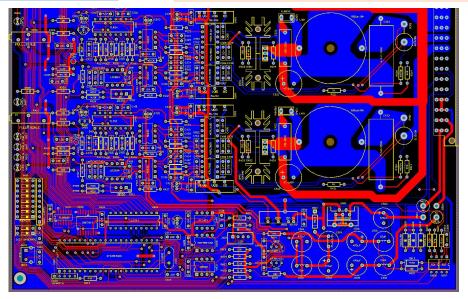

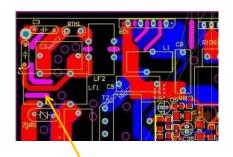

#### E. 大功率/高压隔离

一款程控大功率电源及控制板(局部)

85

# 三、设计步骤和规范

### 【PCB范例】

#### E. 大功率/高压隔离

一款隔离IO输入板(1kV隔离耐压)

# 千万不要相信自己!

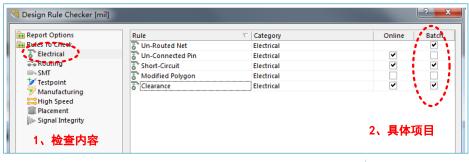

### 1、设计规则检查(DRC, Design Rule Check)

#### 必须检查的三项:

- (1) Electrical -> Un-Routed Net: 未完成的布线的网络。

- (2) Electrical -> Short-Circuit: 两个不同网络之间的短路。

- (3) Electrical -> Clearance: 安全间距不足的布线

89

# 三、设计步骤和规范

### 1、设计规则检查(DRC,Design Rule Check)

#### 建议检查的四项:

- (4) Routing -> Width: 检查线宽是否符合设定范围;

- (5) Routing -> Routing Via Style: 检查过孔尺寸是否符合设定范围;

- (6) Placement -> Component Clearance: 检查元件之间的间距是否足够;

- (7) SMT->SMD To Corner: 检查所有贴片器件引出线是否够长。

#### 注音.

- 规则检查是建立在规则编辑器的基础上的!

- 切勿"削足适履",试图修改规则来使得规则检查通过!

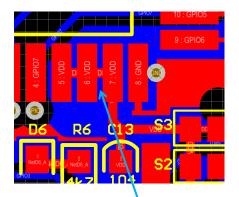

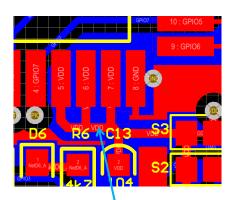

## 2、其他细节的检查

### A. 表贴元件避免焊盘间的连线

焊盘间的线,会给焊接质量 的视觉检查带来困惑

修改后的焊盘间连接线

91

# 三、设计步骤和规范

### 2、其他细节的检查

### B. 避免锐角连线

焊接时,热应力下易断

修改后的电路布线

### 2、其他细节的检查

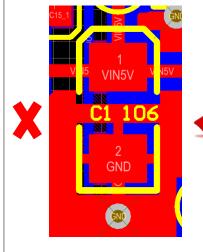

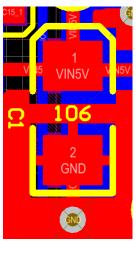

#### C. 注意标号被遮蔽

标号C1 焊接完后被元件遮挡, 检修时困惑

标号必须在器件轮廓之外

93

# 三、设计步骤和规范

### 2、其他细节的检查

### D. 注意字符和焊盘的冲突

焊盘是裸露的,无法印字

实际效果, 文字被"切"

修改后的字符

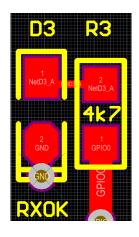

### 2、其他细节的检查

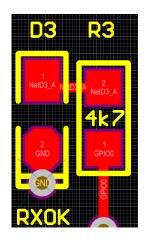

#### E. 细小零件避免出线粗细差异

R3两侧出现粗细差异太大,加热不均匀可能引起翘起(学名:曼哈顿现象;业界俗称"立碑"现象)

修改后

95

# 三、设计步骤和规范

## 2、其他细节的检查

#### F. 热风空隙

热风 缝隙

视频: 左右焊盘加热 不均匀的后果

高大的表面贴装元件,可能会遮挡回流焊的热风,造成局部加热不足虚焊 不得过于紧密地排布

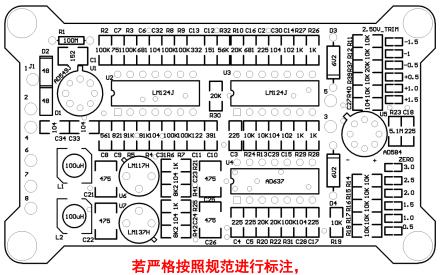

### 3、生成装配图

右严格按照规范进行标注, 打印顶标层(TopOverlay)即可作为装配图使用

97

# 三、设计步骤和规范

# 4、准备物料单(BOM, Bill of Material)

表 5-2 物料清单范例。

| 4    |                   |                          | •          |      |     |              |             |   |

|------|-------------------|--------------------------|------------|------|-----|--------------|-------------|---|

| 类型。  | 型号/值。             | 标号。                      | 封装。        | 数量。  | 误差。 | 备注。          | 供货商/订货号。    | ٥ |

| 电。阻。 | 1k₽               | R21、R25-R29。             | 1206₽      | 6∘   | 1%₀ | 温漂 50ppm/℃。  | 得捷,XXX-XXX。 |   |

|      | 5.1M <sub>e</sub> | R23.                     | 1206       | 1.0  | 5%  | 温漂 50ppm/℃。  | 得捷,XXX-XXX。 | , |

|      | 8.2k              | R41、R42。                 | 1206       | 2.0  | 1%₀ | 温漂 50ppm/℃。  | 得捷,XXX-XXX。 | 0 |

|      | 10k∘              | R11-R19、R24、<br>R39、R40。 | 1206       | 12.0 | 1%€ | 温漂 50ppm/℃。  | 得捷,XXX-XXX。 |   |

|      | 20k₽              | R30.                     | 1206       | 1.0  | 1‰  | 温漂 50ppm/℃。  | 得捷,XXX-XXX。 | ŀ |

|      | 100M <sub>e</sub> | R1.                      | AXIAL0.4   | 1.   | 5%0 | 温漂 100ppm/℃。 | 得捷,XXX-XXX  | P |

| 电感。  | 100uH∘            | L1 、L20                  | 7x7x5 SMD. | 2.0  | 5%- | -40-85℃,封闭式。 | 得捷,XXX-XXX  |   |

|      | 470uH.            | L3.                      | 7x7x5 SMD. | 1.   | 5%. | -40-85℃,封闭式。 | 得捷,XXX-XXX  | ٠ |

| ,    |                   |                          |            |      |     |              |             |   |

推荐这种BOM单格式,既可作为装配使用,也可作为采购用

# 恭喜, 您已经入门

# 然而,仅仅布通还远远不够……

### Part1: 通用电路篇

- 一、引言

- L、PCB基础知识

- 三、PCB设计步骤和规范

- 四、电流路径分析

- 五、常见类型电路设计

# 四、电流路径

大地上的河流九曲十八弯, 看似 走了很多不必要的弯路: 其实

它自己找到了阻力最小的路径!

101

# 四、电流路径分析

- 4.1 电流路径的基本原理

- 4.2 信号环路与回流路径

- 4.3 公共路径与接地问题

- 4.4 电源路径与退耦问题

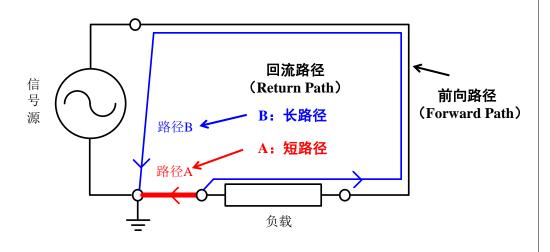

### 1、从一个简单的实验开始

思考: 电流趋向于从哪条路径回流信号源?

103

# 四、电流路径分析

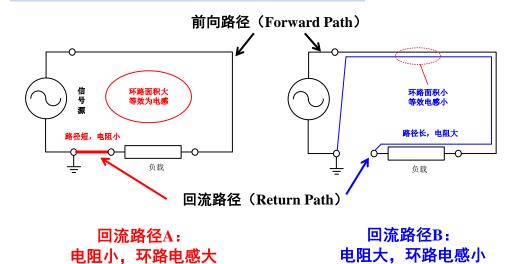

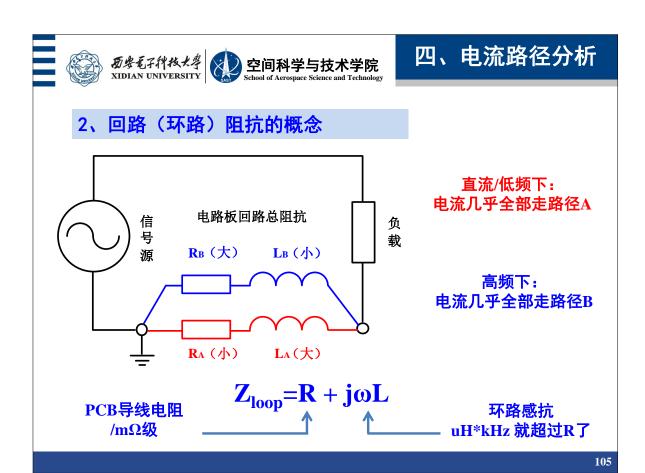

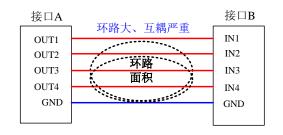

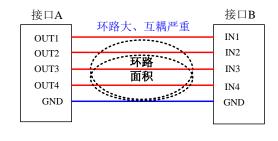

### 2、回流路径与环路阻抗的概念

### 3、环路阻抗(感抗)对信号的影响

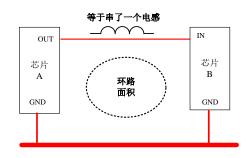

信号线看似很短很直,但是 引入了较大的环路感抗

多路信号线的环路之间的互 感,造成相互干扰

### 注意: "接地"的概念要被颠覆

回流路径! (Return Path)

- 原理图上接地标记无法表示回流路径,误导了版图设计/分析

- 电源在交流等效接地,因此VCC/VDD/VEE也可以作为AC回流路径

### 1、降低回流路径阻抗的意义

#### A. 减少回路感抗

减小回流环路面积, 能够有效降低感抗分量

109

# 四、电流路径分析

### 1、降低回流路径阻抗的意义

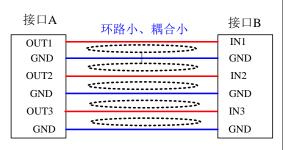

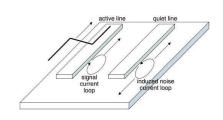

#### B. 减少信号交叉干扰

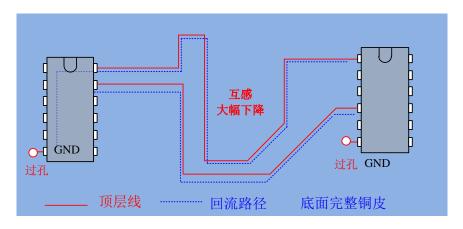

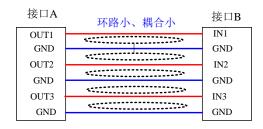

为每一个前向信号配置就近的回流路径,不仅能够减小环路感 抗,还能有效降低环路之间的互感

### 1、降低回流路径阻抗的意义

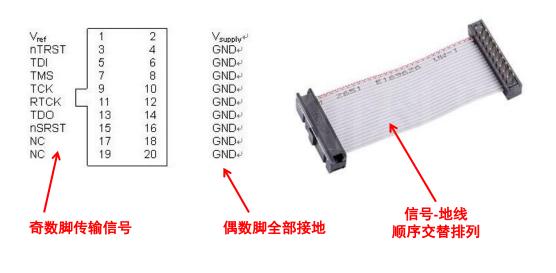

#### 例:排线的交替接地布置

111

# 四、电流路径分析

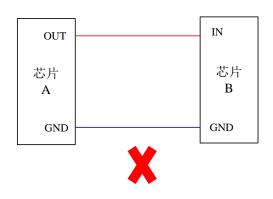

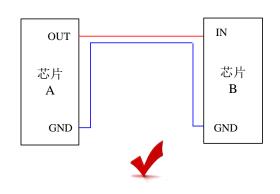

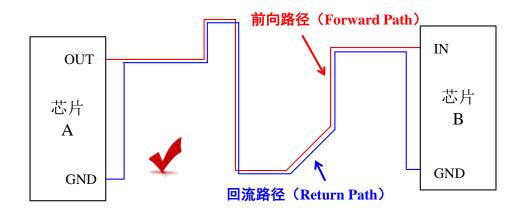

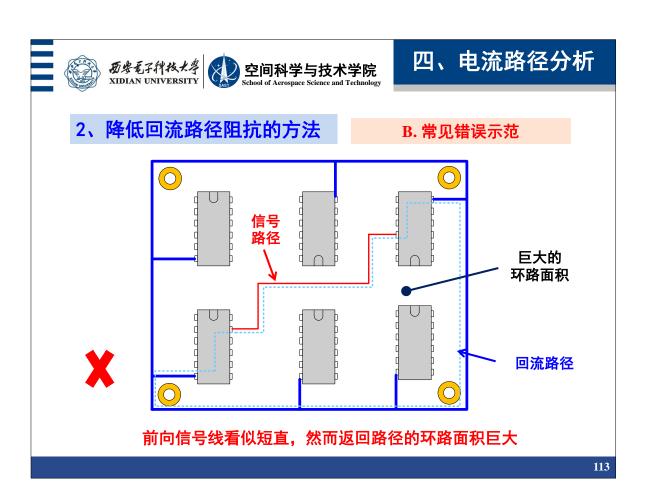

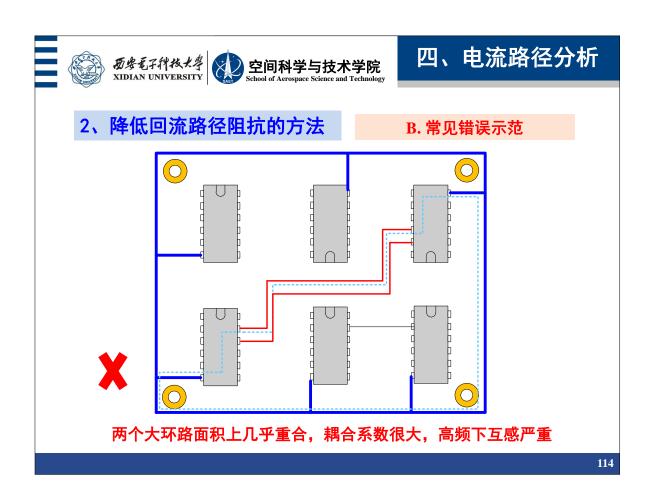

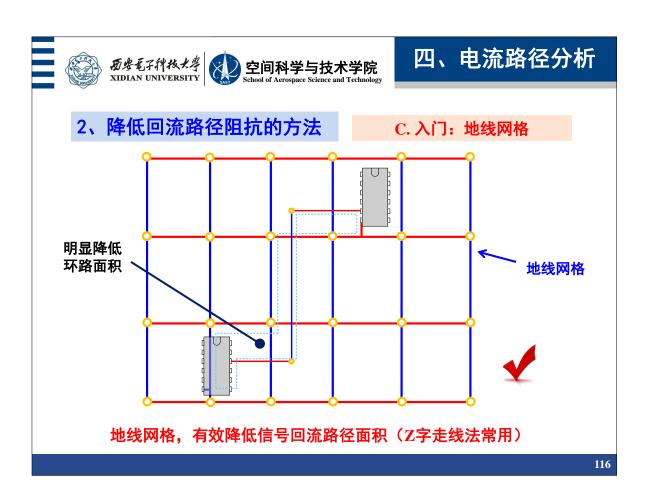

### 2、降低回流路径阻抗的方法

#### A. 指导性原则

不要怕信号线长、不要怕曲折,但一定要为之提供一条 环路面积小(低环路阻抗)的回流路径

### 2、降低回流路径阻抗的方法

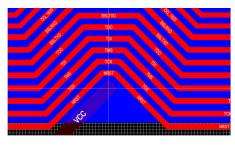

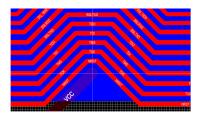

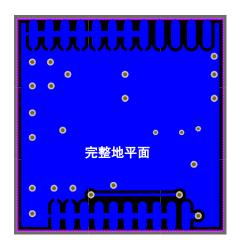

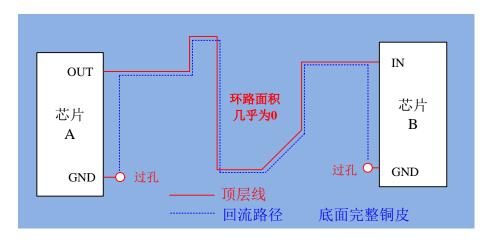

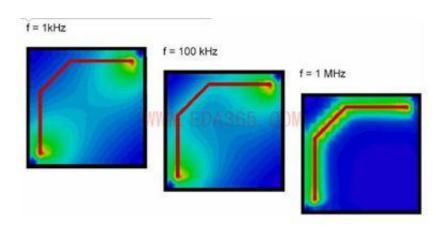

### D. 进阶: 低阻抗平面

在布线区域保留一个完整的导电平面(低阻抗平面),在其上方任意 走线, 电流都能自动得找到最小环路回流路径(在信号线正下方)!

117

# 四、电流路径分析

### 2、降低回流路径阻抗的方法

#### D. 进阶: 低阻抗平面

地平面上方不同频率信号, 在地平面上的回流电流密度分布

### 2、降低回流路径阻抗的方法

#### D. 进阶: 低阻抗平面

回流路径位于信号线正下方,大幅降低了相邻导线之间的互感

\*注:电源VCC平面同样也可以作为低阻抗平面使用

119

# 四、电流路径分析

## 2、降低回流路径阻抗的方法

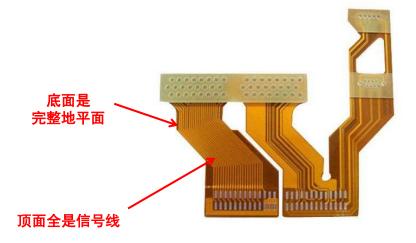

#### 例1: 柔性PCB排线

### 2、降低回流路径阻抗的方法

#### 例2. 多层板的电源层

#### 多层PCB的内部结构

多层板每个信号层下方都衬有有完整低阻抗平面,这样信号层 任意曲折走线都能保证回路面积很小(即使采用自动布线)

121

# 四、电流路径分析

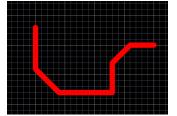

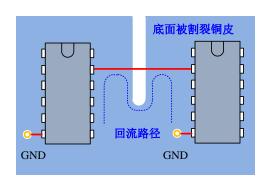

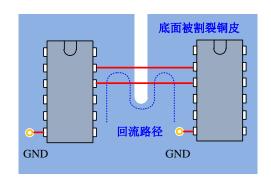

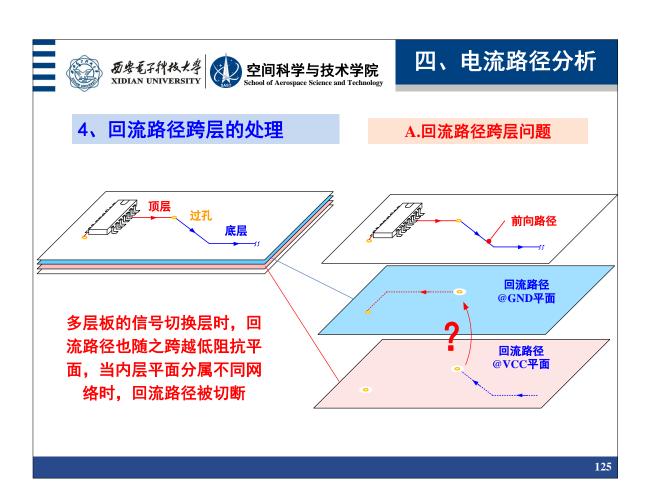

### 3、低阻抗平面的割裂问题

#### A: 信号线跨过割裂缝

导线跨过割缝,回流路径绕行, 将引入额外的回流面积

平行导线跨过割缝,回流绕行路径重叠,将引入额外的互感

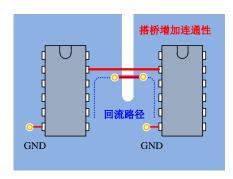

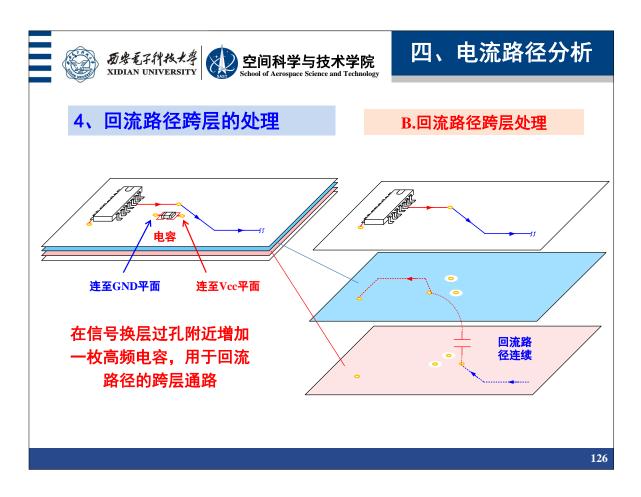

### 3、低阻抗平面的割裂问题

#### B: 割裂缝的缝补

另一面用短线+过孔搭桥, 增加地平面连通性

利用另一面的铺铜进行搭桥, 增加地平面连通性

123

# 四、电流路径分析

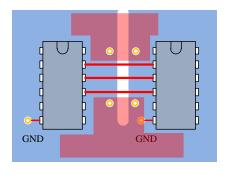

### 3、低阻抗平面的割裂问题

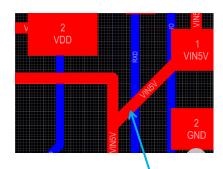

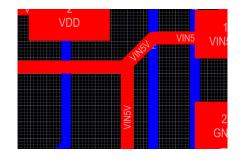

C.底层割裂缝处理案例

合理布局+连通性好的地平面,双面板也有可能接近多层板的效果!

底面几条长电源线造成的 地平面割裂

顶面搭桥位置示意图

### 5、小结

- (1) 信号的回流路径,往往比前向路径更重要!

- (2) 信号趋向于走阻抗(电阻+电抗)最小的路径回流

- (3) 高频下环路感抗起到了决定作用,而前向和回流路径的 环路面积决定了感抗

- (4) 完整的低阻抗平面,能够有效地减小环路阻抗

- (5) 回流路径若被切断,要通过各种手段缝补使之连通

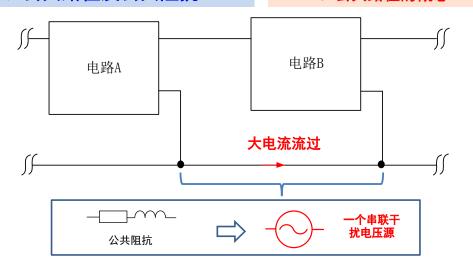

### 1、公共路径及公共阻抗

#### A: 公共路径的概念

大电流通过某些电路之间的公共路径时,其阻抗引起的压降会叠加 在环路中, 引起相互干扰

129

# 四、电流路径分析

### 1、公共路径阻抗的概念

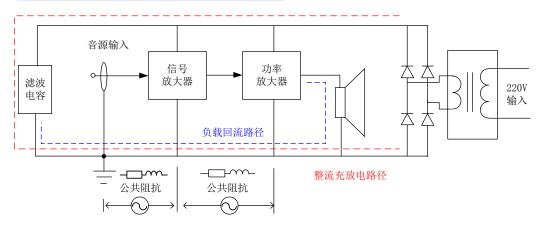

#### B: 地线公共路径的例子

- 滤波电容充放电的电流,流过了敏感的信号放大器地线-><mark>交流声</mark>

- 喇叭回流电流,流过了信号放大器的地线 -> 额外反馈,自激振荡

### 1、公共路径阻抗的概念

#### B: 地线公共路径的例子

#### 原理图完全未变,仅仅通过拓扑结构的变化,消除了公共路径影响

- 充放电回路单独成环、喇叭大电流单独回流; 互不影响

- 小信号部分有公共路径,但其中没有大电流流过

131

# 四、电流路径分析

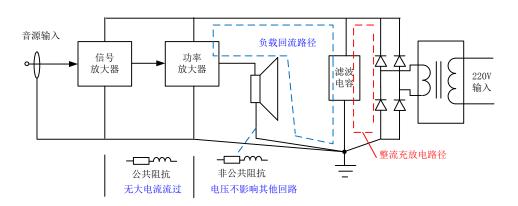

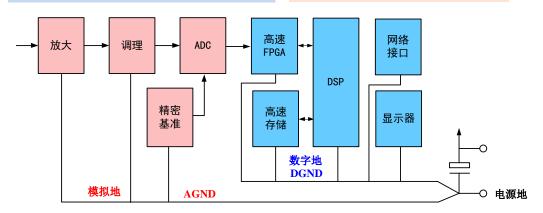

### 1、公共路径阻抗的概念

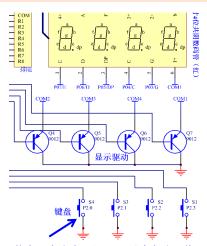

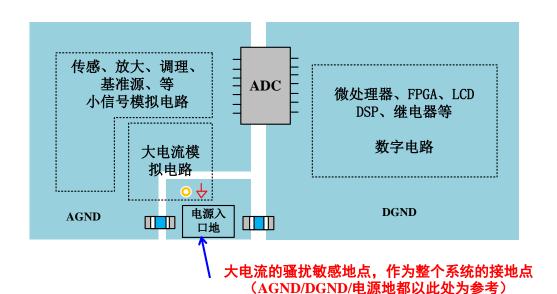

#### C: 模数混合电路的例子

- 混合电路中,将敏感部分和干扰强烈的地线分开,消除了公共路径

- 但我们强烈建议不要用"模拟地""数字地"的名称(定势误解为模 拟电路和数字电路的地线, 实际并不一定)

### 2、接地点的分类

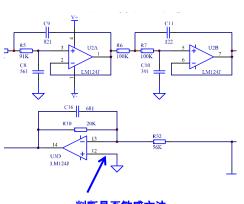

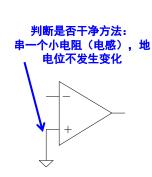

判断是否敏感方法: 若串一个小电压源,电路性能立刻恶化

#### 敏感地:

地电位轻微偏移也不可容忍

#### A: 按照敏感程度分类

若串一个小电压源, 不影响电路工作

非敏感地:

容许地电位较大范围偏移

133

# 四、电流路径分析

### 2、接地点的分类

小信号放大器 接地点

小电流 直流接地点

#### 干净地:

电流小、频率低(或直流),接 地点电位几乎不变化

### B: 按照对外干扰分类

大功率、大电流接地点

#### 骚扰地:

有高频/大电流,会引起接地点 附近地电位变化

### 2、接地点的分类

#### 干净-敏感地

- 模拟前端

- 高倍信号放大 小信号输入

- 精密测量电路

- 电流采样器

- 电源输出端反馈 参考点

骚扰-敏感地

### C: 接地点的分类组合

#### 干净-非敏感地

- 低频数字逻辑

- 低精度模拟电路 粗略门限电路

- 大幅度的模拟电路

- 电磁运动机构

- 喇叭、加热器

- 大电流开关

- **5速数字电路**

- 单片机、DSP、FPGA

骚扰-非敏感地

135

# 四、电流路径分析

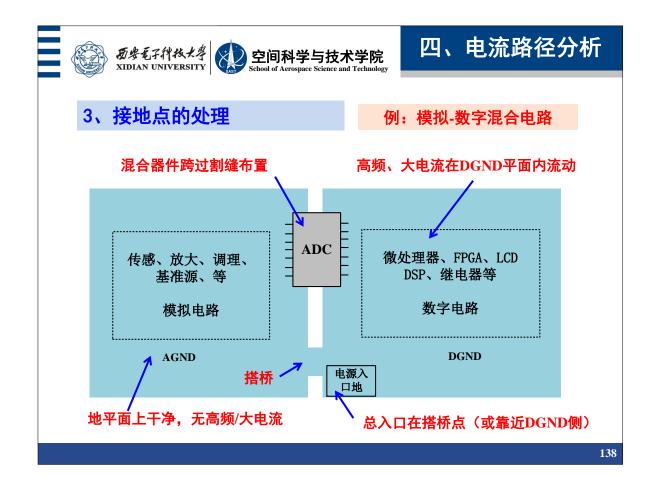

### 3、接地点的处理

#### A: 干净的非敏感地

- 最容易——接到哪里都行

- 允许和敏感地连接在一起

- 也可以和干扰地接在一起

- 看布局方便而定

#### B: 干净的敏感地

- 可以将这些敏感地尽可能近 地连在一起

- 通过铺铜等手段尽可能降低 各接地点之间的阻抗

- 尽量避免其他电流流经敏感 地所在区域

### 3、接地点的处理

#### C: 骚扰的非敏感地

- 避免骚扰地和敏感地有任何 的公共路径

- 将这些接地点单独连在一起,

- 最后一并连到电源入口处。

- 若只有少数骚扰非敏感地,

可将其单独回流至电源入口

#### D: 骚扰的敏感地

- 最难处理——自己骚扰自己

- 若只有一个骚扰敏感点:将此 处点作为整个系统的接地点

- 若有多个骚扰敏感点:隔离和 差分几乎是唯一手段

### 3、接地点的处理

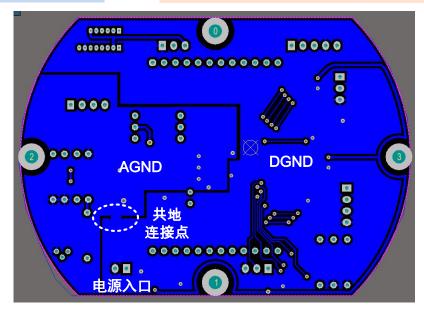

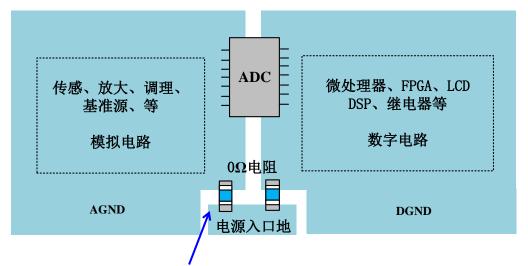

例:模拟-数字混合电路

用0欧电阻搭桥,能避免PCB规则检查的报错(两个网标不允许直接短路)

139

# 四、电流路径分析

## 3、接地点的处理

#### 讨论1: 跨越两个地的信号线

跨越两个地的信号线,要从搭桥的上方走线,方可保证回流路径不被割裂

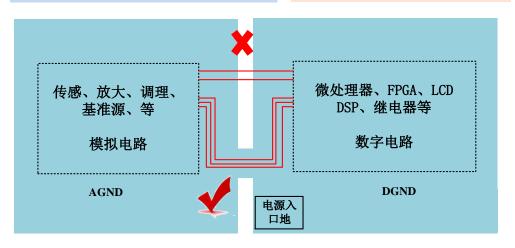

### 3、接地点的处理

讨论2: 是否要用磁珠搭桥?

#### 如何取舍?

- 磁珠的感抗能抑制高频、射频段的地线杂波干扰

- 磁珠对所有跨越割缝的信号线产生很大的(不必要的)感抗 ¥

141

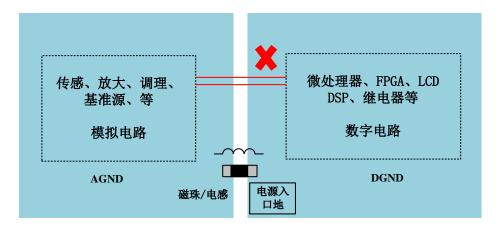

# 四、电流路径分析

### 3、接地点的处理

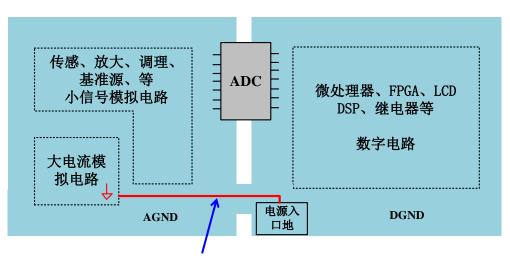

讨论3:模拟部分有骚扰地

大电流模拟电路部分的接地, 单独地拉一条回流线至电源入口

### 3、接地点的处理

讨论4: 模拟部分有骚扰敏感地

143

# 四、电流路径分析

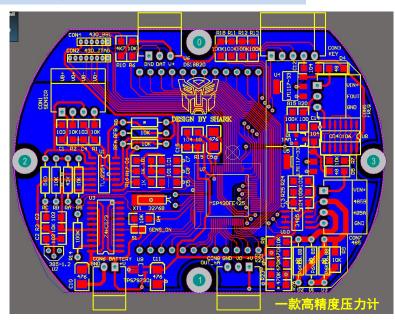

### 4、模拟-数字混合电路设计范例分析

## 4、模拟-数字混合电路设计范例分析

145

# 四、电流路径分析

## 5、小结

- (1) 公共阻抗+大电流流过=相互干扰源

- (2) 地线分为: 敏感、非敏感、骚扰、干净四类组合

- (3) 保证敏感地点尽可能接近零电位,是最主要目标

- (4) 避免骚扰地的回流电流经过过敏感地部分,是主要手段

- (5) 跨接地线割缝的信号线,要避免割缝对回流路径影响

- (6) 慎重使用磁珠连接

# 录

# 四、电流路径分析

- 4.1 电流路径的基本原理

- 4.2 信号环路与回流路径

- 4.3 公共路径与接地处理

- 4.4 电源路径与退耦问题

147

# 四、电流路径分析

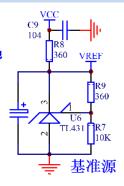

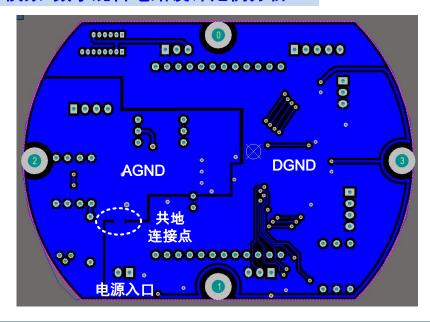

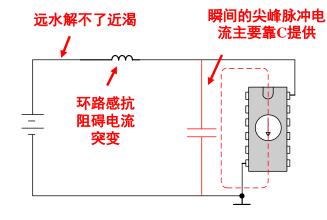

## 1、电源路径有关的概念

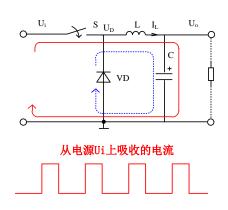

A: 数字芯片的工作电流

- 数字电路的电流波形都是大电流脉冲尖峰,即使是低功耗芯片;

- 每一次逻辑翻转,都会伴随电流尖峰产生,测到的是其平均值;

- 脉冲尖峰电流波形中,包含大量的高频分量! (与工作频率无关)

## 1、电源路径有关的概念

#### B: 模拟器件的工作电流

#### 模拟放大基本单元的工作电流

# +Vcc Vcc电流 输入信号

#### 电源变换基本单元的工作电流

- 模拟器件的工作电流与其信号频率有关,且对于单边电源来说呈脉动状态

- 功率变换/开关电路,呈现周期性的脉动电流(可能还伴随强烈的高频干扰)

149

# 四、电流路径分析

## 1、电源路径有关的概念

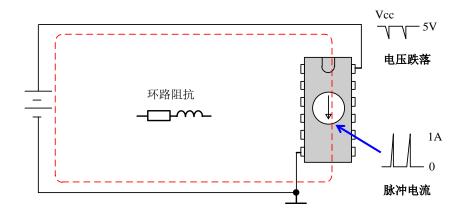

#### C: 电源的环路阻抗与纹波

- 尖峰(高频)脉冲电流,流经环路感抗时造成电源瞬间跌落,引起电源纹波

- 对于高频尖峰,电源路径的阻抗以环路感抗为主,加粗导线无用

## 1、电源路径有关的概念

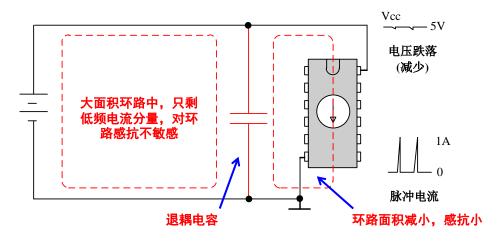

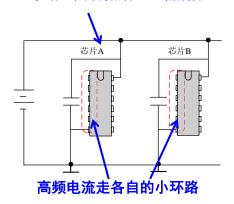

#### D: 退耦的概念

- 对于尖峰(高频)脉冲电流,退藕环路面积小、感抗小

- 电源至退藕电容只剩低频分量,对感抗不敏感,简单加粗导线即可

151

历安笔子科技大学 XIDIAN UNIVERSITY

# 四、电流路径分析

## 1、电源路径有关的概念

#### D: 退耦缓解电源线公共阻抗影响

#### 所有高频电流都走干路,互相影响

#### 环路阻抗1 环路阻抗2 \_\_\_\_ \_\_\_\_ $\nabla \nabla$ 电压跌落 芯 片 - $\mid$ - $\mid$ 0 脉冲式耗电

#### 干路上只剩低频、直流成分

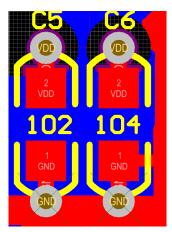

- 退耦电容就近放置——并非距离近,而是电容到芯片电源脚环路面积尽可能小

- 干线只剩低频/直流分量,对环路面积不敏感,简单加粗降低电阻即可。

## 2、电源退耦的要求

#### A: 对退耦电容的容量要求

含义:全靠C储能电压跌落 不超过5%能抗多久

$$\delta t = 0.05 \times \frac{V^2}{P} \times C$$

● 工作电流脉冲持续时间越长、功耗越大、电压越高。所需的电容值越大

153

# 四、电流路径分析

## 2、电源退耦的要求

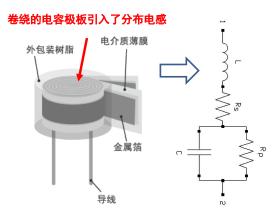

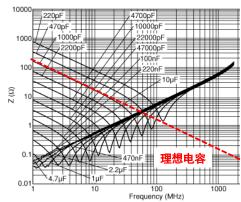

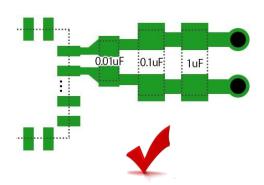

## B: 对退耦电容频率特性的要求

● 大容量电容反而高频特性差,

- 例:村田RCER71系列电容的阻抗特性曲线

- 高频阻抗要足够低: ESR要小; ESL小谐振点高

- 通常会通过大小电容并联来保证低频和高频下都有足够低阻抗

## 2、电源退耦的要求

#### B: 对退耦电容特性的要求

表 1. 电容的谐振频率

| 电容值     | 通孔插装 (0.25 引线) | 表面贴装 (0805) |

|---------|----------------|-------------|

| 1.0 μF  | 2.5 MHz        | 5 MHz       |

| 0.1 μF  | 8 MHz          | 16 MHz      |

| 0.01 μF | 25 MHz         | 50 MHz      |

| 1000 pF | 80 MHz         | 160 MHz     |

| 100 pF  | 250 MHz        | 500 MHz     |

155

#### 历安笔子科技大学 XIDIAN UNIVERSITY

# 四、电流路径分析

小电容

C2

C2

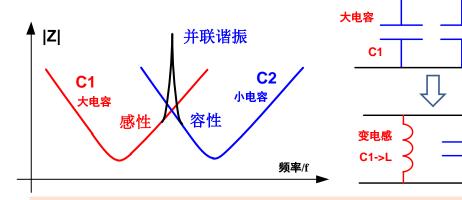

## 2、电源退耦的要求

## B: 对退耦电容频率特性要求

- 大电容呈电感特性,小电容仍然容性,两者可能会构成并联谐振电路

- 在谐振点处,将会呈现高阻抗特性——几乎呈断路,该频点信号无法穿过

- 当两个电容差别3个数量级以上时,要特别小心(不建议3数量级以上并联)

## 2、电源退耦的要求

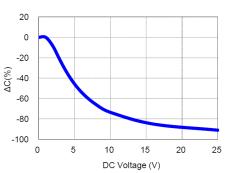

# DC Bias Characteristic

一枚50V-II类陶瓷的直流偏压效应 (电容量随直流偏压急剧下降一半)

DC Bias/V

#### C: 注意陶瓷电容的偏压效应

一枚25V-III类陶瓷的直流偏压效应 (电容量随直流偏压急剧下降至10%)

- ||-|||类陶瓷介电系数随着场强增加而急剧下降, 电容量也随之下降

- 额定电压下,Ⅱ类陶瓷损失一半左右容量,Ⅲ类陶瓷损失容量90%以上

- 在退耦、隔直应用时,必须在设计时考虑余量,容忍直流偏压效应引起的损失

157

-10

-15

-20

-25 -30

-35 -40

-45

-50

Cap. Change/%

面安笔子科技大学 XIDIAN UNIVERSITY

# 四、电流路径分析

## 2、电源退耦的要求

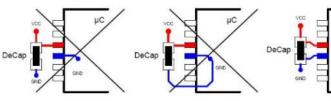

#### D: 对电容摆放位置的要求

退耦路径的环路面积尽可能小,比电容和芯片实际空间距离更重要

## 2、电源退耦的要求

#### D: 对电容摆放位置的要求

多个电容并联时, 小容量的电容应更靠近芯片电源引脚

159

# 四、电流路径分析

## 电源退耦的要求

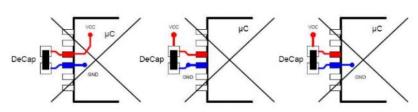

#### 常见错误分析

- a) VCC and GND lead to supply noise current flows not via DeCap, DeCap has not effect

- b) GND lead noise to system GND noise current flows partly via DeCap, DeCap has hardly effect

- c) GND lead noise to System GND noise current flows partly via DeCap, DeCap has hardly effect

- d) VCC and GND lead to supply noise current flows not via DeCap, DeCap has not effect

- e) GND is not short connected to DeCap. between GND and DeCap flows a loop current DeCap has hardly effect

- f) DeCap correct connected to μC and power supply.

high speed current will be supported from DeCap

## 3、多层板的退耦

#### A: 退耦半径的概念

退耦半径 IC都从电源平面上取电

- 在有完整电源平面的情况下,一个电容可以为附近的IC提供退耦

- 一枚电容能够提供优良退耦效果的区域半径, 称为退耦半径

161

# 四、电流路径分析

## 3、多层板的退耦

B: 退耦半径的计算

电容退耦半径 = 谐振频率对应波长/(40-50)

#### 【例1】

1nF陶瓷电容, ESL=1.6nH, 谐振频率为125MHz, 谐振周期为 8ps。假设信号在电路板上的传播速度为65.3ps/cm,则波长为120cm。电容去耦半径为120cm/50=2.4cm, 大约等于 2.4厘米。

#### 【例2】

10uF电解电容谐振频率为800kHz,按上述过程计算退耦半径约3.7米

结论: 小电容应尽量靠近芯片引脚,大电容对位置不太敏感; 又为了避免充放电电流经过整板,通常把大电容放在电源入口处

## 3、多层板的退耦

#### C: 降低过孔引入的寄生电感

引入额外环路寄生电感

● 就近接电源层,尽可能较少引出线带来的额外环路面积

● 严禁多个电容共用过孔! (引入公共路径感抗)

163

# 四、电流路径分析

## 3、多层板的退耦

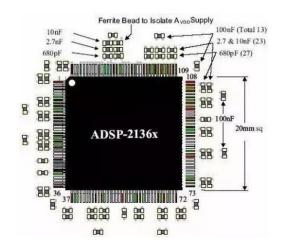

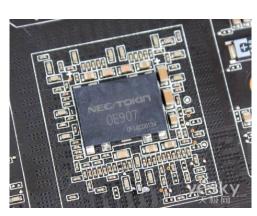

#### 电源退耦电容布局实例

ADI高速DSP推荐的退耦电容布局

华硕GTX系列显卡芯片背面的退耦电容布局 (中间OE907是一枚大电容)

## 1、敏感电路

光电探测转换电路(弱信号)

#### A. 常见的敏感电路

精密仪器(准确度)

传感器 (分辨率)

敏感电路:容易受干扰的电路部分

167

# 五、常见类型PCB

## 1、敏感电路

#### B. 敏感电路的考量

- 是否容易受干扰

- 对干扰的容忍度

- 是否在干扰源附近

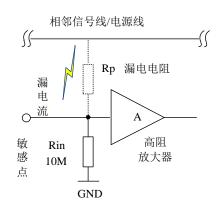

#### D. 电路受干扰的原因

- 来自空间电场耦合、

- 来自磁场耦合、

- 来自电路板绝缘不良的漏电电流。

#### C. 常见敏感电路位置

- 微弱信号线

- 高阻抗点

- 放大器前级输入端

- 传感器信号

- 大功率电路附近的检测电路

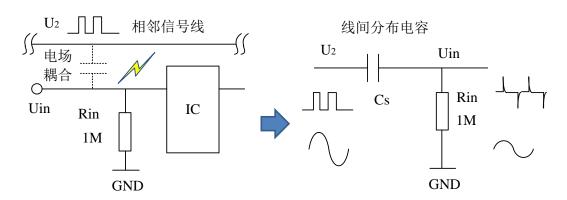

## 2、电场耦合干扰

#### A. 电场耦合干扰的概念

- 机理:干扰源的电力线跨过导线间的分布电容,和被扰线对地阻抗构成分压关系

- 干扰源线的距离越近、频率越高,越容易干扰(容抗越小)

- 被干扰线对地的阻抗越高,越容易受干扰 (阻抗越高)

169

面安笔子科技大学 XIDIAN UNIVERSITY

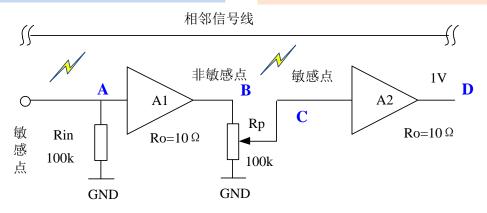

# 五、常见类型PCB

## 2、电场耦合干扰

#### B. 电场敏感节点的判断

节点的对地的等效阻抗越高,就越容易受到电场干扰。

A点: 输入开路状态高阻是敏感点(接入理想电压源后,变为非敏感点)

B点/D点: 运放输出端, 低阻抗点, 非敏感点

C点: 电位器拧到两侧时为非敏感点, 电位器在中点时, 为敏感点

## 2、电场耦合干扰

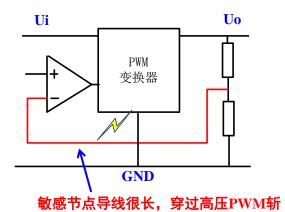

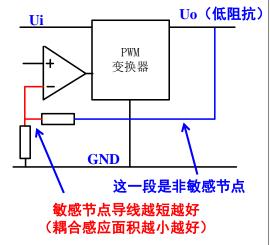

#### C. 敏感节点的处理

171

波部分的下方, 易受电场耦合干扰

#### 历安毛子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

## 2、电场耦合干扰

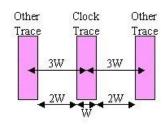

#### D. "3W/10W"原则

- 3W原则: 导线中心间距为线宽3倍以上时,可以 避开70%的电场耦合;

- 10W原则: 导线中心间距为线宽10倍以上时,可以避开98%的电场耦合;

## 2、电场耦合干扰

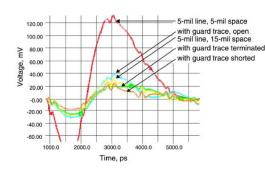

#### E. 防护布线

- 在敏感线与相邻线之间增加接地线,称为防护布线,能进一步降低电场耦合

- 防护布线要加上接地短路过孔(严禁悬空),否则干扰反而增强

173

#### 历安笔子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

## 3、磁场耦合干扰

#### A. 磁场耦合干扰的来源

公共耦合环路面积

互感干扰

## 3、磁场耦合干扰

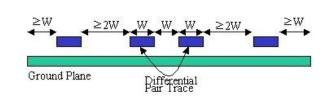

#### B. 减少磁场耦合干扰的方法

配置回流路径,降低公共耦合 环路面积

增大微带线间距,或改为带状线 (电流对称,磁力线抵消)

175

面安笔子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

## 4、电路板漏电影响

#### A. 电路板漏电的影响

PCB表面污染和体电阻漏电 电流对高阻抗节点的干扰

| Val NAVA CO    | 处理条件                     | 单位      | 性能参数             |                     |

|----------------|--------------------------|---------|------------------|---------------------|

| 测试项目           |                          |         | 参考数值             | 典型数值                |

| Tg             | DSC                      | °C      | ≥130             | 140                 |

| 可燃性            | C-48/23/50               |         | V-0              | V-0                 |

| 9.9MX 1-32     |                          |         |                  |                     |

| 体积电阻系数         | 浸水后                      | MΩ-cm   | ≥106             | $2.0 \times 10^{8}$ |

| 体供电阻杂数         | E-24/127                 |         | >10 <sup>3</sup> | 5.0×10 <sup>8</sup> |

| # W + PD 27 #4 | 浸水后                      | MΩ      | ≥10⁴             | 3.0×10 <sup>7</sup> |

| 表面电阻系数         | E-24/125                 |         | ≥10 <sup>3</sup> | 5.0×10 <sup>7</sup> |

| 抗电弧性           | D-48/50+D-0: 5/23        | S       | <b>≱</b> 60      | 115                 |

| 介质击穿           | D-48/50+D-0. 5/23        | KV      | ≥40              | 55                  |

| 介电常数(1MHZ)     | 0-24/23/50               | 10      | ≤5.4             | 4. 7                |

| 介质损耗角(1MHZ)    | 0-24/23/50               | 10      | ≤ 0. 035         | 0. 01               |

| 挽曲强度 横向        |                          | No.     | ≥415             | 450                 |

| 抗田強度 纵向        | A                        | Mpa     | ≥345             | 400                 |

| 吸水率            | D-24/23                  | %       | ≤ 0.5            | 0.1                 |

| C1             | JPCA-ES-01-2003-standard | %       | ≤ 0.09           | 0.05                |

| Br             | JPCA-ES-01-2003-standard | %       | ≤ 0.09           | 0                   |

|                |                          |         |                  |                     |

| 备注:所有的测试数据都    | 符合 IPC-4101/92 标准        |         |                  |                     |

| 样品厚度: 1.6mm    |                          |         |                  |                     |

| 说明:C=潮湿条件 D=沉  | 曼在蒸馏水条件 E=温度条件           |         |                  |                     |

| Tg=玻璃化转化温)     | 度, 板材在高温下产生软化变形并伴随       | 着机械及电气性 | 主能的急剧下降.         |                     |

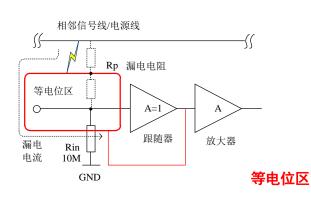

对于10M以上高阻抗点,就要开 始考虑PCB漏电的影响

## 4、电路板漏电影响

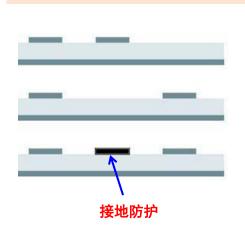

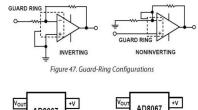

####

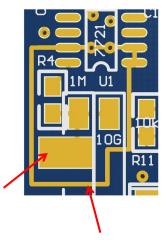

保护环,将漏电电流吸收至地 (适合保护低电压或虚地点)

GND

GND

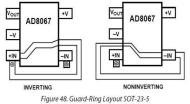

#### B. 保护环(Guard Ring)

保护环的画法,将敏感部分完全包围

177

历安笔子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

## 4、电路板漏电影响

## C. 等电位保护

等电位保护环,用低阻抗跟随器制 造等电位区并将漏电电流吸收

保护环的导线应裸露,以增加吸收表 面污染泄露电流的能力

## 4、电路板漏电影响

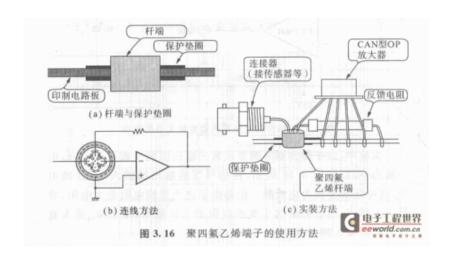

#### D. 隔离岛和聚四氟乙烯端子

敏感局部使用绝缘性能极佳的聚四氟乙烯端子,避免与PCB接触

## 1、常见涉及高压的电路

功率电源/逆变电路

隔离接口

可能接入未知电压的继 电器/开关等

插板式变压器/ACDC输入端

升压/局部高压偏压电路

181

# 五、常见类型PCB

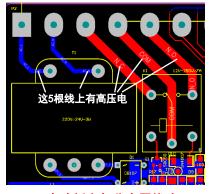

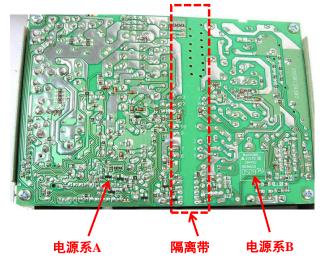

## 2、高压电路的布线

高压隔离槽,能有效增加防爬 弧距离,防止污染降低绝缘性

## A. 高压隔离槽

高压隔离槽的画法: 在KeepOut层画粗线;注意宽度>1mm否则 不便下刀

## 2、高压电路的布线

#### A. 高压隔离槽

#### 对于典型220VAC电源系统、I类电气设备的安全间距

| 位置      | 开槽    | 不开槽   |

|---------|-------|-------|

| L线-N线   | 2.0mm | 2.5mm |

| 电源-外壳/地 | 2.0mm | 2.5mm |

| 变压器隔离两侧 | 4.4mm | 6.0mm |

| 隔离两侧电路  | 4.0mm | 5.0mm |

#### 对于典型 36-76V DC/DC系统, I类电气设备的安全间距

| 位置      | 开槽    | 不开槽   |

|---------|-------|-------|

| +/-电源线  | 0.7mm | 1.4mm |

| 电源-外壳/地 | 0.7mm | 1.4mm |

| 隔离两侧电路  | 1.4mm | 2.8mm |

<sup>\*</sup>更详细的安全距离标准,请参考IEC/EN/UL60950-1

183

# 五、常见类型PCB

# 2、高压电路的布线

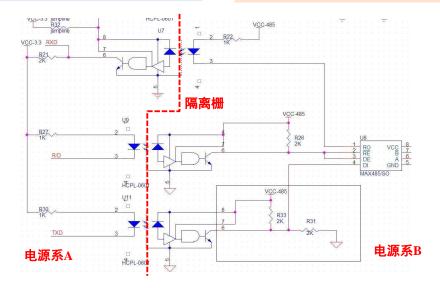

#### B. 电源系的概念

隔离电路中,分属不同电源系的任何两根线之间,都要满足绝缘要求

#### C.隔离带

- 分属不同电源系的任何两根线 之间。

- 都要满足绝缘要求

185

# 五、常见类型PCB

# 2、高压电路的布线

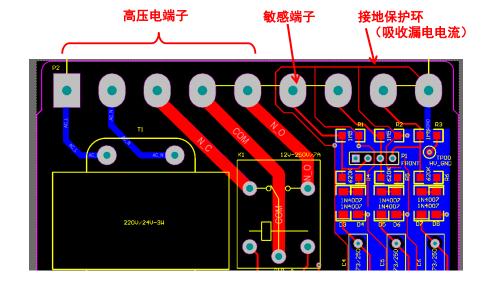

#### D.PCB漏电与保护环

## 1、大电流部分的处理

#### A. 回顾:线宽与电流关系

【例】导线通过10A电流,在室温25℃工作 时要控制导线表面温度不超过70℃

#### 【解】

- (1) 允许温升70-25=45℃。

- (2) 查曲线横截面积 s=150mil<sup>2</sup>

- (3) 厚度1Oz (35um,1.38mil) 的PCB, 则最小线宽是150/1.38=108mil;

- (4) 采用2Oz的电路板,需要54mil线宽。

- 采用增加导体厚度、改善对流条件,可减小线宽需求

- 大电流过孔计算: 查表所需横截面s, 孔周长l=s/0.7-1.0mil(18-25um);孔径d=l/π

189

历安笔子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

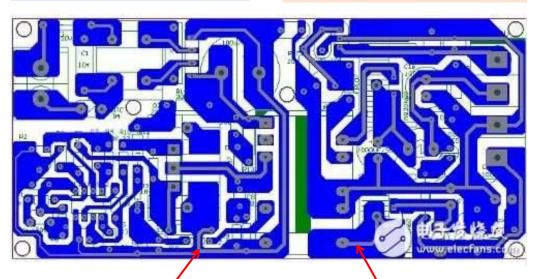

# 1、大电流部分的处理

## B. 布线风格

Step1: 用导线完成布通

Step2: 用Fill+Reigion 充分利用铜箔导电面积

## 1、大电流部分的处理

#### C. 镀锡(增加导体厚度)

在大电流导线所在的 Top/Bot Solder 层绘制导线

实际效果:用波峰焊工艺处理后,裸 露部分挂锡,增加导电层厚度

- 镀锡后的导线等效截面积可增大约1.5-2倍

- 手工堆锡、埋焊铜丝等方法,等效截面积可增大5-10倍

191

历安冠子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

## 1、大电流部分的处理

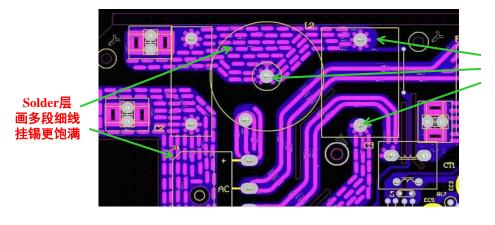

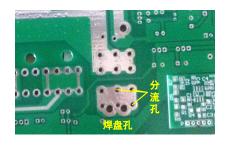

## C. 镀锡(增加导体厚度)

大电流焊点 四周镀锡

- 大面积镀锡,容易流动,挂不均匀;改为多段细线,挂锡饱满效果更好

- 大电流焊点,要加分流镀锡,避免电流密度过高局部烧断

## 1、大电流部分的处理

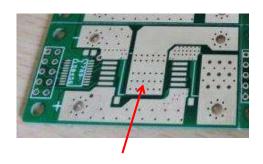

#### D. 过孔和分流孔

大电流导线上的过孔需要很大的直径,可分散成许多小孔

大电流元件引脚换层时,电流可能过于 密集,在附近要考虑增加分流孔

193

#### 面字笔子科技大学 XIDIAN UNIVERSITY

# 五、常见类型PCB

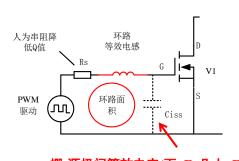

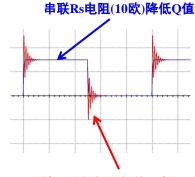

## 2、高频开关电路设计考虑

## A. 开关驱动环路

栅-源极间等效电容(百pF~几十nF)

直接驱动栅极的振铃现象

- 让驱动环路面积(驱动器OUT->MOS栅->源极->驱动器GND)尽可能小

- 栅极串阻的作用:降低环路Q值,避免过冲损坏栅极或错误开关动作

- 栅极串阻会降低开关速度,要实测找到速度和过冲平衡点【不要照抄参考设计】

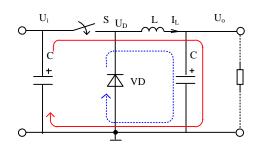

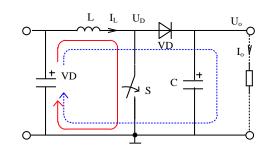

## 2、高频开关电路设计考虑

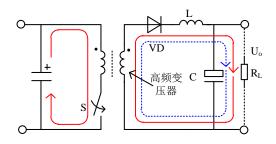

#### B.储能环路和续流环路

- (a) Buck电路中的储能和续流环路

- (b) Boost路中的储能和续流环路

- Step1: 对照拓扑结构图,找出开关变换器的储能环路和续流环路

- Step2:布线应让储能和续流环路的面积都要尽可能小

- Step3:检查储能环路及续流环路与其他导线之间的耦合

195

历安笔子科技大学

# 五、常见类型PCB

## 2、高频开关电路设计考虑

#### B.储能环路和续流环路

- (c) Forward电路中的储能和续流环路

- (d)) Flyback电路中的储能和续流环路

- Step1: 对照拓扑结构图,找出开关变换器的储能环路和续流环路

- Step2:布线应让储能和续流环路的面积都要尽可能小

- Step3:检查储能环路及续流环路与其他导线之间的耦合

## 2、高频开关电路设计考虑

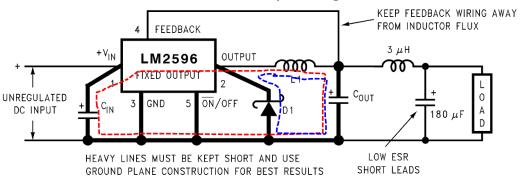

#### C. 开关环路分析案例

#### **Fixed Output Voltage Versions**

---- 开关ON/储能环路

197

# 五、常见类型PCB

# 2、高频开关电路设计考虑

#### C. 环路面积控制案例