# TI 电量计 PCB Layout 设计指导

张楚涛 Hugo Zhang

TI电量计产品技术支持

## 摘要

TI 的单节和多节电量计产品以其出色的性能,在消费类和工业类应用,如手机,笔记本,穿戴式设备,电动工具等电池包里被广泛应用。因为这些应用中通常都是大电流充放电回路和低功耗小信号电路混合在同一块PCB 板上,所以 PCB layout 的好坏对其性能有很重要的影响。本文介绍了在使用 TI 电量计时,PCB layout 设计的注意事项。

## **長**目

| 1, | <b>陇辽</b>   | <u> </u>                  | 2 |

|----|-------------|---------------------------|---|

| 2, | 与E          | :SD 相关的 PCB layout 注意事项   | 2 |

|    | 2.2         | 1,电池包简化电路描述               | 2 |

|    |             | 2,打 ESD 时电流走向分析           |   |

|    |             | 3,让 IC 远离大电流充放电回路         |   |

|    |             | 4,单点接地的考虑                 |   |

|    |             | 5,ESD 放电气隙(Spark Gaps)    |   |

| 3. |             | 上能相关的 PCB layout 注意事项     |   |

| -, |             | 1,电源管脚的退耦电容               |   |

|    |             | 2,通讯线上的防护器件               |   |

|    |             | 3,开尔文连接和 Board Offset 的考虑 |   |

|    |             | 4, 地平面的设计考虑               |   |

| 4. |             |                           |   |

|    |             | 当<br>当                    |   |

| _  | J /         | H                         |   |

|    |             |                           |   |

|    |             |                           |   |

|    |             | 图                         |   |

| 图  | 1: 🗏        | 电池包的电路框图                  | 2 |

| 冬  | <b>2:</b> ? | 生连接器 PACK+打 ESD 时的电流走向    | 3 |

|    |             | 生连接器 PACK-打 ESD 时的电流走向    |   |

| 冬  | 4: 7        | 生连接器通讯线上打 ESD 时的电流走向      | 4 |

|    |             |                           |   |

|    |             | 大电流充放电回路和低功耗小信号电路的布局      |   |

|    |             | 作单点接地时可能会导致电量计损坏          |   |

| 图 8: | 正确的单节接地的接法              | 6 |

|------|-------------------------|---|

|      | 电池包连接器上放电气隙 layout 的示意图 |   |

|      | : 电源管脚上退耦电容的布局和走线       |   |

|      | : 电流检测电阻的 RC 滤波电路的布局布线  |   |

|      | : 单点接地和地平面的设计考虑         |   |

#### 1, 概述

本文将分别从与 ESD 相关和与性能相关两个方面来详细讨论 TI 电量计在 PCB layout 上需要注意的事项,并配以相应的 layout 示意图来详细说明。

## 2,与 ESD 相关的 PCB layout 注意事项

## 2.1, 电池包简化电路描述

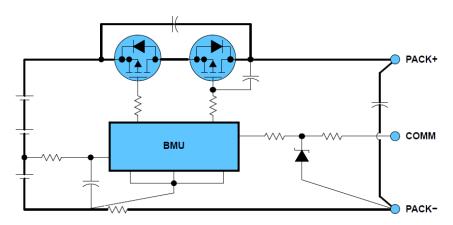

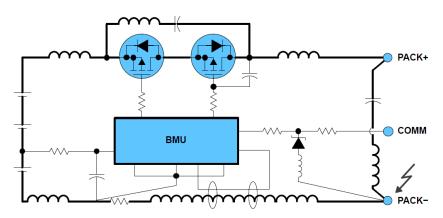

下图是一个典型的电池包的简化电路框图,包括电芯,电量计(BMU)及其周边电子元器件,连接器等。下面我们将用这个简化电路框图来讨论对电池包打 ESD 时的情况。

在电量计(BMU)周边,有电芯,保护 MOSFET,电流检测电阻,连接器等。在电量计左边的 RC 滤波电路是代表多个 RC 滤波电路,用于监控多节电芯的电压。电量计下方的连接代表多个从电量计及其周边电子元器件连接到单点接地的地。该单点通常是从电流检测电阻与电芯最负端(B-)连接的焊盘上引出。在电量计右边的电阻和稳压管代表多个通讯线上的 ESD 防护网络。

图 1: 电池包的电路框图

## 2.2, 打ESD 时电流走向分析

在打 ESD 时,ESD 电流通常会流向最大容值的地方,即电芯上。而且 ESD 电流会选择阻抗最低的路径。所以宽的走线或敷铜,因为其低阻抗和低感抗,可以把 ESD 电流引导到电芯上,从而避免 ESD 电流窜到其他 ESD 敏感的电子元器件,导致器件损坏。

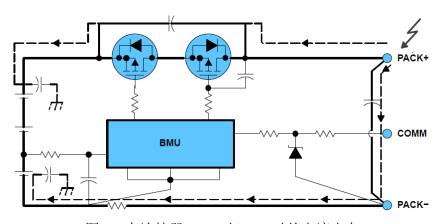

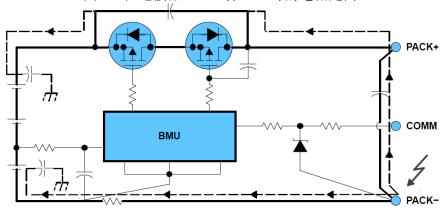

图 2 和图 3 是在 PACK+和 PACK-打 ESD 时电流的走向。这两种情况,电流的路径是类似的。因为本身要走大电流,所以 MOSFET 的走线或覆铜会比较宽。而并联在 MOSFET 两端的电容(通常是两个串联,以防止其中一个电容短路导致保护功能失效),因为其交流短路的特性,会对 MOSFET 形成保护。但前提是连接电容的走线或覆铜也尽量宽和尽量短。

PACK+和 PACK-上的电容(通常是两个串联,以防止其中一个电容短路导致失效)也同样重要。在 PACK+端打 ESD 时,这些电容提供了分流的支路。连接这些电容的走线或覆铜也尽量宽和尽量短。

图 2: 在连接器 PACK+打 ESD 时的电流走向

图 3: 在连接器 PACK-打 ESD 时的电流走向

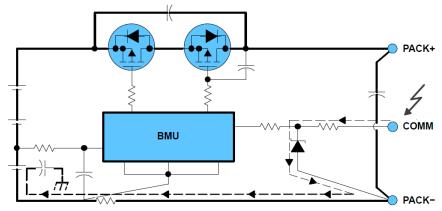

图 4 是在连接器通讯线上打 ESD 时的电流走向。同样,也需要给 ESD 电流提供一条到电芯的低阻抗通路。如下图所示,ESD 电流会先通过串联的电阻,然后再通过稳压管的结电容,到达 PACK-,最后到达电芯。所以 layout 布局时要把稳压管靠近连接器。

图 4: 在连接器通讯线上打 ESD 时的电流走向

#### 2.3, 让IC 远离大电流充放电回路

虽然大电流充放电回路尽量宽的走线或覆铜可以提供低阻抗和低感抗的通路,但在 ESD 脉冲频率(GHz)下还是会呈现出感性的特性。在 ESD 脉冲频率下,这些走线或覆铜会形成耦合变压器的原边,如图 5 所示,从而耦合到旁边的走线(耦合变压器的副边),从而影响或损坏相应的 ESD 敏感元器件。

图 5: ESD 时高频电流感性耦合

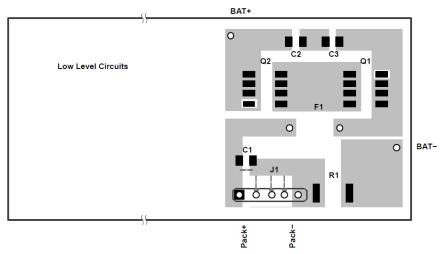

为了尽量避免大电流充放电回路和低功耗小信号电路之间的耦合,最优的做法就是如图 6 所示,把大电流充放电回路和低功耗小信号电路在空间上左右分开,而且分别分布在 PCB 板的顶层和底层。虽然在实际项目中会受到很多限制,没法达到这种理想的情况。但是还是需要尽可能做到,从而尽可能降低大电流充放电回路和低功耗小信号电路之间的耦合。

图 6: 大电流充放电回路和低功耗小信号电路的布局

## 2.4,单点接地的考虑

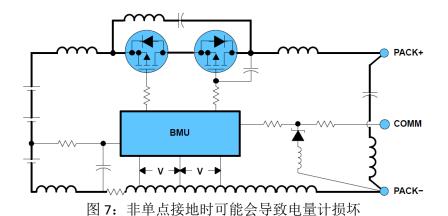

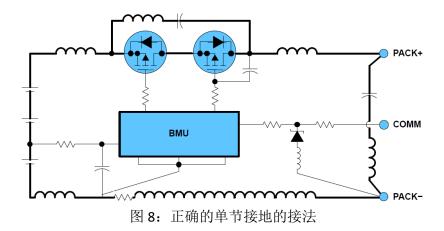

根据公式 V=L\*di/dt, 电流的变化率很大时, 会产生很高的感应电压。如果 layout 时没有做好单点接地,可能 会在打 ESD 时在各个接地点之间产生感应电压的压差,如图 7 所示,从而导致电量计损坏。正确的单点接地 可以参考图8。

TI 电量计 PCB Layout 设计指导 5

## 2.5,ESD 放电气隙(Spark Gaps)

放电气隙对于打 ESD 时保护连接器上的通讯线是非常有效的。请参考下面图 9 的 PCB layout 示意图。两个三角尖峰的间距建议是 10-mil(0.25-mm),这间距可以提供大概 1500V 的击穿电压。使用放电气隙需要注意,不能在三角尖峰上敷绿油,要让三角尖峰的金属裸露在空气中。而且那些三角尖峰不能被板上其他物体(如连接器)覆盖,所以放电气隙要放在连接器的另一面。即如果连接器是放在 TopLayer,那放电气隙要放在BottomLayer。

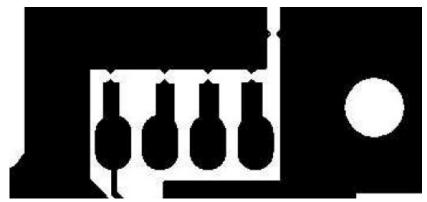

图 9: 电池包连接器上放电气隙 layout 的示意图

## 3,与性能相关的 PCB layout 注意事项

#### 3.1,电源管脚的退耦电容

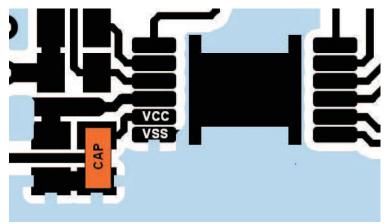

对电量计电源管脚上的退耦电容,需要尽量靠近电源管脚。这可以让环路面积最小。大的环路面积可能降低电容退耦的作用。理想情况是电容两端的 PCB 走线等长,而且是并排走线。这可以避免打 ESD 时的差分噪声。

图 10: 电源管脚上退耦电容的布局和走线

#### 3.2,通讯线上的防护器件

通常在通讯线(I2C 或 SMBus)上用 T 型 ESD 防护电路,即两个电阻串联,中间接一个稳压管或 TVS 管。使用 T 型 ESD 防护电路,在布局上建议两个电阻分别靠近芯片的管脚和靠近连接器端。而中间的稳压管或 TVS 管则建议靠近连接器端。对于单节电量计用在 low side 保护的电池包,建议 TVS 的阴极接在 B-端,可跨过 low side MOSFET,快速泄放 ESD。

## 3.3,开尔文连接和 Board Offset 的考虑

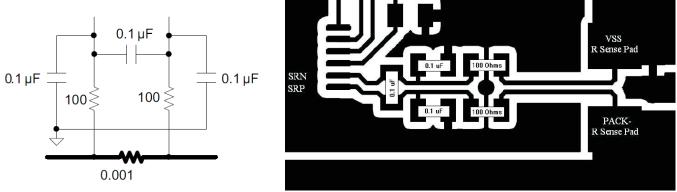

电量计的电流测量是通过检测电流检测电阻两端的电压来实现的。由于电流检测电阻两端的压差非常小,如 1mOhm 的电阻流过 1A 电流,压差只有 1mV,所以 SRN/SRP 管脚很容易受干扰。

为了确保电流测量的精度,电流检测电阻需要采用开尔文连接(Kelvin Connection),即引到芯片 SRN/SRP 管脚的电流检测线必须从电流检测电阻的焊盘引出,从而避免引入额外的走线阻抗影响测量精度。

一般从电流检测电阻两端到 SRN/SRP 管脚,都会有 RC 滤波电路。为了确保电流测量的精度,对于这些 RC 滤波电路的布局和布线有如下要求:对称布局,差分走线,且确保走线的长度和走线上的过孔个数相同。这样可以尽量避免因为布局布线导致的电流零偏(Offset)的影响。

在允许的情况下,在这些 RC 滤波电路和走线的周围进行 GND 网络的敷铜,从而提高抗干扰的能力。

下面图 11 是在布局和布线上做得比较好的例子。

图 11: 电流检测电阻的 RC 滤波电路的布局布线

#### 3.4, 地平面的设计考虑

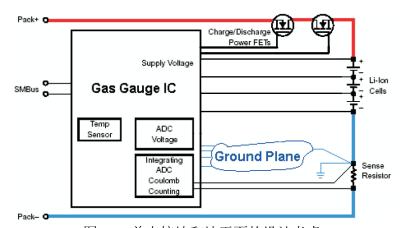

通常电量计应用,都是大电流充放电回路和低功耗小信号电路混合在同一块 PCB 板上。需要特别考虑电量计的地平面的设计。推荐的做法是把大电流充放电回路的地和低功耗小信号电路的地区分开。大电流充放电回路的地是指从电芯最负端(即 B-)到连接器负端(即 P-)之间的走线。这一段走线因为要走大电流,所以要求尽量宽尽量短。低功耗小信号电路的地平面(下图的 Ground Plane)的设计应该遵循单点接地的原则,如图 12 所示,即该地平面必须从开尔文连接的同一个点用细线引出,然后所有低功耗小信号电路的地都接在该地平面上。一定要避免该地平面有多个连接点与 B-网络相连。

图 12: 单点接地和地平面的设计考虑

#### 4, 总结

本文分别从与 ESD 相关和与性能相关两个方面来详细介绍了 TI 电量计在 PCB layout 上需要注意的事项。本文 所介绍的 PCB layout 布局布线上的经验已经在很多手机和笔记本电池包上实践并证明有效。同时相关经验也 适用于工业类电池包。

## 参考文档

Single Cell Impedance Track Printed-Circuit Board Layout, <a href="https://www.ti.com/lit/pdf/slua457">https://www.ti.com/lit/pdf/slua457</a>

bq20z70/90 Printed-Circuit Board Layout Guide, <a href="https://www.ti.com/lit/pdf/slua392">https://www.ti.com/lit/pdf/slua392</a>

Avoiding ESD and EMI Problems in bq20zxx Battery Pack Electronics, <a href="https://www.ti.com/lit/pdf/slua368">https://www.ti.com/lit/pdf/slua368</a>

## 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司